WIMAX LDPC碼譯碼器的FPGA實現

2 WIMAX 標準的LDPC碼譯碼器設計

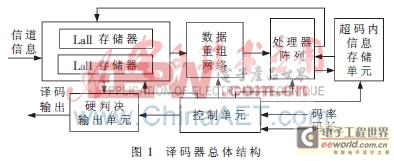

2.1 譯碼器總體結構

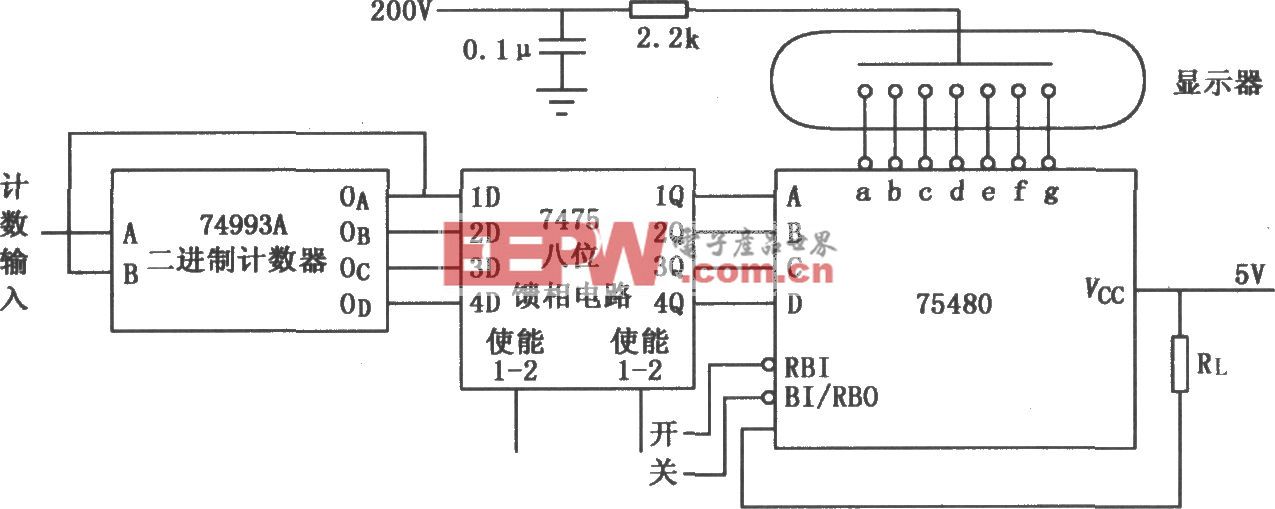

根據前述TDMP-NMS譯碼算法, 本文設計的部分并行LDPC碼譯碼器結構如圖1所示。整個譯碼器由后驗LLR存儲單元、數據重組網絡、處理器陣列、硬判決輸出單元及控制單元構成。為支持連續譯碼,信道信息的存儲由2組相同的工作于乒乓讀寫模式的RAM完成。數據重組網絡根據校驗基矩陣中對應的數值對從后驗LLR存儲單元輸出的z個數據進行循環移位后送入處理器陣列中相應單元進行處理。處理器陣列由96個相同的處理器單元構成,當擴展因子為z時,僅使能其中的z個處理單元,并行處理更新對應于1個超碼的z個SPC碼。 控制單元產生各個模塊的工作使能信號和控制信號。采用最大迭代次數停止準則,當譯碼迭代次數達到設定的最大值時,硬判決輸出單元對從后驗LLR存儲單元中讀出的信息進行硬判決并輸出譯碼結果。

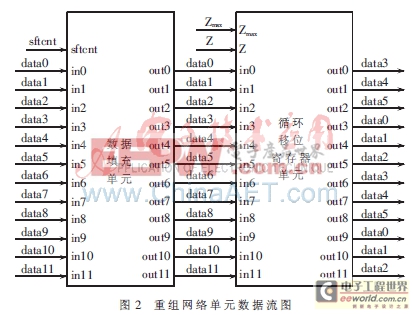

2.2 重組網絡的設計

本設計所提出的重組網絡單元結構支持對輸入數據個數為該網絡輸入輸出端口數的因子的數據序列的循環移位。該結構由數據填充單元和桶形移位寄存器單元構成。為支持最大擴展因子zmax=96碼長的LDPC碼, 本設計中桶形移位寄存器單元的輸入輸出數據端口數均為96。填充單元在預處理階段用并行輸入的z個有效數據填充桶形移位寄存器的所有96個輸入端口,第nz+i個端口用第i個有效輸入數據填充。其中n=0,1,…,(96/z)-1,i=1,…,z。桶形移位寄存器單元對這96個數據根據輸入的循環移位值控制信號進行循序移位。移位結束之后,輸出端口的前z個數據即為所需的數據序列。一個輸人輸出數據端口數均為12的重組網絡,當有效輸入數據個數為6,循環移位值為3時,數據流圖如圖2所示。

每次迭代處理過程中,傳遞給處理器陣列的每個單元處理的變量節點后驗LLR值是經過數據重組網絡循環移位后的數據序列。為使下一次迭代處理時輸入至該單元的數據是按原始順序排列的序列[4],采用了兩個重組網絡,一個用于將從變量節點LLR存儲器中的讀出數據進行重組,另一個用于將處理更新后的LLR后驗數據進行反重組。為了降低硬件實現的復雜度,同時減少單次迭代處理所需的時鐘周期,提高譯碼器吞吐率,本設計將采用一種增量循環移位的方案[5]。采用該方案,每次對從存儲器中讀出的z個變量節點后驗LLR信息循環移位的值是本次該組數據所需移位的值與上一次所需移位值的模z的差值。經處理器陣列處理更新后的后驗LLR值不經過重組網絡直接存儲至原單元。

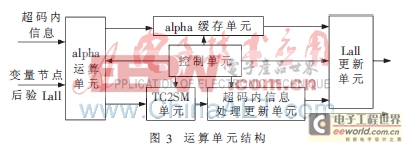

2.3 運算單元設計

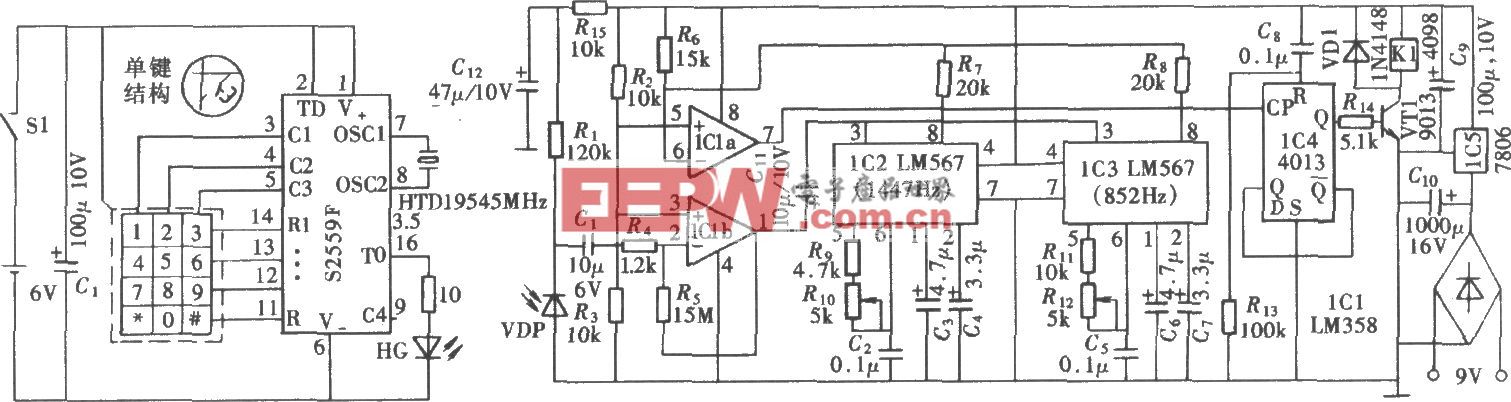

為使譯碼器能夠支持WIAMX標準中的所有6種碼率, 本文設計了如圖3所示的基于串行處理的運算單元結構。其中alpha 運算單元接收以壓縮形式輸入的本超碼的內信息ri,0,ri,1,ind_min,sign_j和變量節點j的后驗LLR信息Pj,根據式(1)和式(2)計算出qij。qij一路傳遞給alpha緩存單元用于后續的后驗LLR更新,一路傳遞給TC2SM轉換模塊,將以二進制補碼表示的qij轉換為符號-絕對值的表示形式,并傳遞給超碼內信息處理更新單元。該單元每個周期接收一個幅度值和符號值,根據該幅度值與當前最小值min0和次小值min1的比較結果更新min0,min1,ind_min,將接收到的符號值存儲于寄存器并執行模2累加運算。當對應于一個校驗節點的所有變量節點信息接收完畢,開始執行min0,min1的歸一化操作計算ri,0和ri,1,以及sign_j的更新。該運算完成之后開始從alpha緩存單元中順序讀出之前存儲的qij,根據(6)(7)完成變量節點后驗LLR值Pj的更新。控制模塊的作用主要是根據當前超碼校驗節點的度數產生計算qij和更新ind_min、Pj時所需的當前變量節點的序號和各個模塊的工作使能信號。為減少控制單元的扇出,本設計中采用8個運算單元共享一個控制單元的模式,整個處理器陣列96個運算單元共使用了12個控制單元。

2.4 變量節點后驗LLR信息的讀取

對WIMAX 標準中碼率為1/2 和2/3B的LDPC碼,通過改變各個超碼的迭代處理順序,可以使得任何兩個相鄰的超碼沒有公共的變量節點,因此當前超碼的處理不用等到前一個超碼迭代處理結束。在本設計中,當前一個超碼的變量節點后驗LLR從相應的存儲單元讀出完畢一個周期之后即開始讀取當前超碼的變量節點后驗LLR信息。對于其他碼率,通過分析其對應的校驗矩陣的特點,發現同一個變量節點在前后兩個相鄰超碼中的迭代處理順序最大相差3個周期,如圖4中碼率為2/3的A碼第一個超碼和第二個超碼方框內所示的數字對應的一組z個變量節點,在第一個超碼中的處理順序是第8,在第二個超碼中的處理順序是第5。 又由于從當前超碼所有校驗節點相鄰的變量節點后驗LLR讀出完畢至第一組z個更新后的后驗LLR輸出之間相差7個時鐘周期, 為了在當前超碼處理時用到更新后的變量節點后驗LLR信息,本設計在對其他碼率的LDPC碼迭代處理時,當前一個超碼對應的所有變量節點讀出完畢10個周期之后開始讀取下一個超碼的變量節點后驗LLR信息。

3 實現結果及分析

選擇CycloneII系列的FPGA芯片EP2C70F896C6作為目標器件, 編譯綜合后的結果顯示,該譯碼器共消耗27 077個邏輯單元,最高工作頻率可達69 MHz,在該工作頻率下,譯碼器對該標準中碼長為2 304的各碼率的LDPC碼譯碼迭代10次時,所需的譯碼周期數分別為:

1 011、1 686、985、1 520、1 550、1 257,對應的譯碼吞吐率分別為:79 Mb/s、63 Mb/s、109 Mb/s、79 Mb/s、78 Mb/s、106 Mb/s,完全能夠滿足WIMAX標準數據吞吐率的要求。

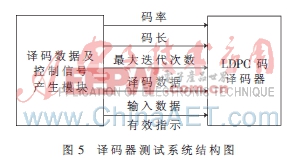

在DE2-70開發板上對所設計的譯碼器進行了硬件測試,測試系統結構如圖5所示。

譯碼數據及控制信號產生模塊產生譯碼器工作所需的譯碼數據和相關的控制信號:碼率、碼長、最大迭代次數、輸入數據有效指示信號。譯碼器根據輸入的數據及控制信號進行譯碼。譯碼數據及控制信號產生模塊中有一個存儲一幀譯碼數據的ROM。為了在Quartus2的SignalTap II Logic Analyzer中觀察到譯碼器的輸出信號,該模塊周期性地從ROM中讀取譯碼數據和產生相應的控制信號。本文對碼率為1/2,碼長為2 304的LDPC碼進行了測試。測試中系統工作頻率為50 MHz,邏輯分析儀的采樣時鐘為100 MHz,由輸入的50 MHz信號經PLL倍頻得到。得到譯碼器的譯碼輸出波形如圖6所示。圖中hdd_en為輸出有效數據指示信號,dout0 ~dout11為譯碼器并行輸出的96 bit數據,將該數據與原信息序列相比較,結果完全相同,譯碼器工作正常。

本文設計實現了一種支持WIMAX標準的碼長、碼率可配置LDPC碼譯碼器,通過設計一種基于串行工作模式的運算單元,實現了對該標準中所有碼率的支持。通過設計一種基于填充算法的重組網絡單元實現了對該標準中擴展因子為24、32、48、96的4種碼長的支持。采用TDMP-NMS算法,在提高譯碼收斂收率的同時,降低了硬件復雜度。實驗結果表明,所設計的譯碼器在50 Hz的時鐘頻率下工作正常,完全能夠滿足WIMAX 標準數據吞吐率的要求。

評論