光電靶的基本原理

1 基于FPGA的嵌入式系統開發流程

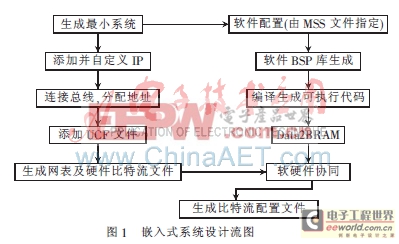

設計一個嵌入式系統,主要包括硬件平臺搭建和應用軟件編寫。基于FPGA技術,硬件平臺搭建和軟件編寫都可在相應的軟件平臺上完成。EDK(Embedded Development Kit)是Xilinx公司開發嵌入式系統的套件工具。EDK套件工具主要包括硬件平臺產生器、軟件平臺產生器、仿真模型生成器和軟件編譯調試等工具,利用其集成開發環境XPS(platform studio)可以方便地完成嵌入式系統的開發設計[1],設計流程如圖1所示。

2 硬件平臺搭建過程

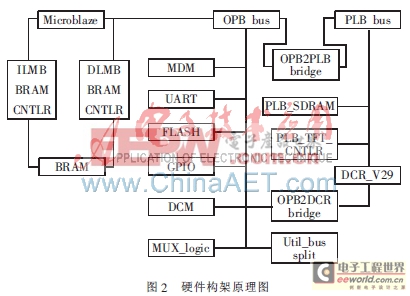

分析系統需求中,鐵軌檢測主要是進行圖像的分析處理,包括三個主要部分:圖像輸入、圖像處理和結果顯示。本項目使用依元素公司生產的Xilinx Spartan-3a系列xc3s700a的FPGA開發板,軟件版本為Xilinx10.1。圖像輸入有下列途徑:USB接口、RS232串口、100 M以太網接口、EDK套件XMD調試平臺直接下載等。本文將圖像數據轉換為.ELF文件格式,直接燒寫入Flash中。本文不追求實現視頻流處理,并且圖像要多次使用,源圖像存儲在Flash中最合理。圖像處理由Microblaze軟核系統和檢測程序共同完成;圖像顯示由TFT控制器通過VGA輸出信號在液晶顯示屏顯示。具體硬件平臺搭建過程如下:

(1)按照XPS應用向導,建立最小系統,配置Microblaze軟核系統參數和添加UART外設。

(2)添加IP核,并連接到相應總線,主要為內存控制器、通信控制和GPIO等。

(3)添加自定義的IP。盡管Xilinx提供了許多免費IP,但是免費的IP不能滿足用戶的所有設計。本項目需要自定義的IP有用于控制液晶顯示的TFT_Controller和用于內存地址總線及數據總線復用的Mux_logic IP。PLB_TFT_Controller主要產生RGB信號、行場掃描、同步信號等,Mux_logic IP用于對SDRAM和Flash總線復用進行控制,輸入為SDRAM和Flash的控制IP產生的地址總線信號和數據總線信號及使能信號,輸出為復用地址總線、數據總線信號。

(4)配置相應IP,并進行信號互聯,將需要控制硬件的port連接到外部。分配地址空間,添加UCF配置文件。

(5)生成硬件比特流文件和硬件驅動文件。硬件結構原理圖如圖2所示。

3 軟件設計過程

3.1 鐵軌檢測原理

本項目中鐵軌檢測主要考慮兩種方案[2]:基于邊緣特征和基于區域特征。(1)基于邊緣特征檢測方法先在全局范圍檢測出邊緣線,再通過模型或特征限制條件,從邊緣圖中獲得目標邊緣。(2)基于區域特征的鐵軌檢測,利用區域統計特性,即鐵軌區域區別于周圍環境獨特統計特性來判斷鐵軌區域。兩種方法中,前者檢測到的鐵軌線較為準確,但是其對二值化閾值嚴重依賴;后者抗噪性較好,但檢測的鐵軌線不夠準確,本文主要討論基于區域特征的鐵軌檢測。

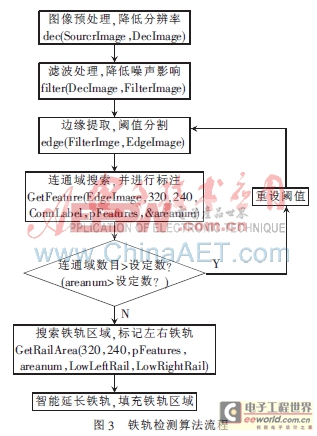

基于區域特征鐵軌檢測流程如圖3所示,分為四個步驟:

(1)降低分辨率。在濾波之前,先降低圖像分辨率,以消除圖像細節,也可減輕后續處理的計算負擔。

(2)濾波處理。分辨率降低后,圖像中仍有很多的突兀點,這是因為鐵軌上各種電磁信號的存在,攝像頭采集到的圖像不可避免地受到高斯噪聲、系統噪聲的污染。考慮到圖像特征,選用中值濾波,它在平滑脈沖噪聲方面非常有效,同時可以保護圖像尖銳的邊緣。

(3)邊緣提取。利用邊緣檢測算子檢查每個像素的鄰域并對灰度變化率進行量化,包括方向的確定。Sobel邊緣檢測算子方向性靈活,可以設置不同的系數,抑制噪聲效果較好,使用范圍廣泛,因此選用Sobel算子。同時鐵軌圖像橫向變化不大,而在縱向有很大的延伸,故也只考慮圖像垂直邊緣響應。

(4)連通域搜索。二值化處理后邊緣圖包含了鐵軌信息,也含有很多非鐵軌邊緣。使用八連通區域搜索法,進行標號處理,記錄相互獨立的連通區域個數并進行標號。對連通區域按照長度大小進行排列,直到搜索出縱向最長的兩根鐵軌,然后判斷并標記左右兩鐵軌,之后進行區域填充,最終可以看到標記的鐵軌區域。

3.2 OpenCV仿真結果

本項目程序首先實現OpenCV仿真,然后移植到FPGA中。OpenCV提供的圖像處理算法非常豐富,并且部分程序以C語言編寫,處理得當,不需要添加新的外部支持就可以完整的編譯連接生成執行程序進行算法移植。本次仿真只運用“cv.h”和“highhui.h”兩個OpenCV庫,主要是運用其圖像加載、圖像顯示等函數,而中值濾波、邊緣檢測、鐵軌搜索函數自行編寫。仿真結果如圖4所示。

3.3 FPGA程序移植過程

3.3.1 圖像輸入與顯示[3]

本項目把圖像數據轉換為.ELF文件格式,燒錄到NOR-Flash,在XPS的菜單下點擊Program Flash Memory,選擇自動格式轉換,即可進行燒錄,而且可以指定燒錄數據的位置。數據格式轉換利用Matlab軟件完成,程序如下:

fid = fopen(′pic.elf′, ′w′);//打開文件

img =imread(′Image03.BMP′);//讀圖像數據

imshow(img);//顯示圖像

fwrite(fid,img.′);//寫數據

fclose(fid);//關閉文件

由于是灰度圖像,只讀取其亮度值。圖像分辨率為640×480。寫數據可以用fprintf函數或fwrite函數,但是實驗表明使用fprintf函數寫數據,文件大小302 kB,顯示圖像不正常;而使用fwrite函數寫數據文件僅300 kB,顯示圖像正常。說明兩種函數寫數據方式本質不同,造成寫入數據格式不同。

圖像顯示過程:先從Flash中每次一行把數據讀入BRAM,然后把每一位亮度值移位變為R、G、B三位,再從BRAM讀數據到SDRAM顯存,如此循環480次,用以顯示圖片。由于R、G、B值相同,顯示的便是灰度圖像。如果直接從Flash讀數據到SDRAM顯存,顯示圖像每行有不規則不連續的黑點,甚至顯示不正常。顯存的設置在TFT-Controller IP中完成,顯存空間為2 MB,起始地址與SDRAM起始地址相同。

3.3.2 圖像處理程序移植[3]

由于開發環境不同,移植后程序在獨立系統上運行,需要對OpenCV仿真程序做一些改正。FPGA編程系統支持C語言標準庫函數,所以打印輸出顯示函數print()、動態內存分配函數malloc()可以直接使用。盡管printf()函數也可以用于打印輸出結果,但目的是把程序放入大小為32 KB的BRAM,實驗表明它比print()函數占用空間大一倍。在OpenCV中,可以直接使用cvShowImage()、cvReleaseImage()、cvDestroyWindow()函數顯示圖像和釋放內存空間,在移植程序中要自行設計這些函數。移植程序中subplot()函數用于在屏幕上顯示4幅圖像(降低分辨率源圖像、濾波圖像、閾值分割圖像、鐵軌檢測圖像),DeleteAllPointElems()函數用于釋放內存空間。其他函數,例如降低分辨率函數Dec()、濾波函數filter()、邊緣檢測函數edge(),可以完全使用OpenCV中的程序,不需要做修改。移植后主程序如下:

int main()

{ print("rn-- Entering main() --rn");

SourceImage=(Xuint8*)malloc(640×480);

DecImage=(Xuint8*)malloc(320×240);

FilterImage=(Xuint8*)malloc(320×240);

EdgeImage=(Xuint8*)malloc(320×240);

ResultImage3=(Xuint8*)malloc(320×240);

//為圖像分配內存空間

if (SourceImage==NULL)

{print("rn--mem allo fail--rn");

exit(1);}//驗證空間是否分配成功

XTft_Initialize(Tft, TFT_DEVICE_ID);

//TFT顯示初始化

XromTftTestColor("black", 0);

//顯示背景設置為黑色

flbuf=(unsigned char*)Flash_BASEADDR;

//設置Flash圖像基地址指針

p=SourceImage;//設置源圖像指針

for (y=0;yHEIGHT;y++)

{rowpoint1=flbuf+y*WIDTH;

for(x=0;xWIDTH;x++)

{data1=*(rowpoint1+x);

*p++=data1;

} }//讀源圖像數據

dec(SourceImage,DecImage);

filter(DecImage,FilterImage,320);

edge(FilterImage,EdgeImage,320);

//圖像降低分辨率、濾波、邊緣化

nt areanum=0;

GetFeature(EdgeImage,320,240,

ConnLabel,pFeatures,areanum);

//邊緣提取,搜索連通域

GetRailArea(320,240,pFeatures,

areanum,lowLeftRail,lowRightRail);

//搜索鐵軌區域,獲得左右軌

int i, j;

for (i=1; i = areanum;i++){

DeleteAllPointElems(pFeatures[i]);}

//釋放內存空間

int Left,Right;

for(i=1;i240; i++){

Left=lowLeftRail[i];

Right=lowRightRail[i];

if((Left>0)(Right>0)){

for(j=Left;j=Right;j++){

*(TrackImage+i*320+j)=255;}}}

//填充鐵軌左右軌之間區域

subplot(DecImage,1);

subplot(FilterImage,2);

subplot(EdgeImage,3);

subplot(TrackImage,4);

//顯示4幅處理圖像

print("-- Exiting main() --rn");

}

FPGA圖像處理結果如圖5所示。

本文實現基于FPGA的鐵軌檢測算法,首先完成OpenCV程序仿真,然后移植到FPGA構建的硬件系統中,可以成功檢測出鐵軌所在區域,并在一定條件下進行鐵軌智能延長。研究結果表明,檢測一幅分辨率為640×480圖像,大約需要30 s,如果應用于實時視頻流系統中,則硬件平臺設計需要進行精簡,以提高速度。也可考慮基于硬核、多核技術,來提高處理速度,以滿足實時視頻流處理。

參考文獻

[1] 趙澤才,常青.基于MicroBlaze的嵌入式系統設計[D].湖南:國防科學技術大學,2005.

[2] 李俊,楊春金.基于邊緣特征及對稱差分的鐵路安全圖像處理技術研究[D].武漢:武漢理工大學,2009.

[3] 楊杰,黃朝兵.數字圖像處理及MATLAB實現[M].北京:電子工業出版社,2010.

評論