關于Verilog簡易UART的FPGA/CPLD實現

可編程語言:Verilog

隨機測試:是

波特率:9600

誤碼率:1%oooooo

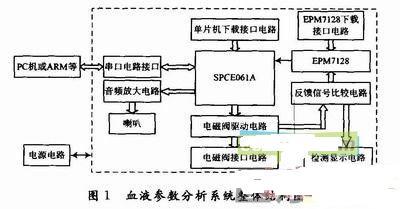

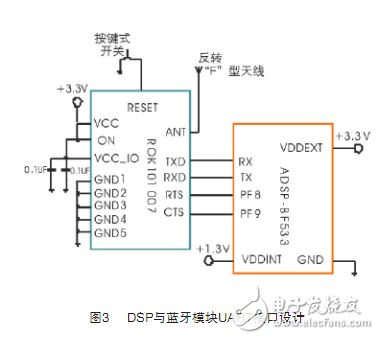

目標:在xo640上實現一個簡單的UART,能夠解析串口數據,并在寄存器中存儲,用FIFO實現數據的傳遞。那么后期可以通過開發板上的串口經CPLD訪問各種數據。比如PC=CPLD=EEPROM等等,極大方便后期的開發和調試。

下面介紹一下重點:

1、Speed波特率及采樣設置

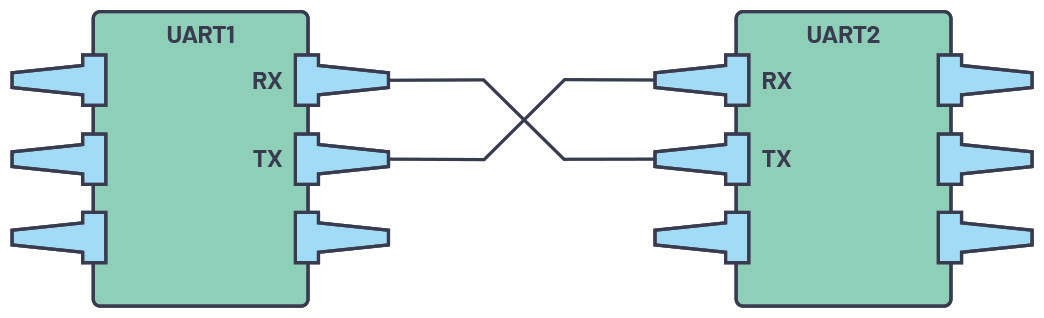

這里的原理是:根據實際的波特率和板卡所使用的晶振頻率,在容許的誤差范圍內(串口有一定的容錯率)進行分頻。這里強調一點,做法可以分為以下兩類:分頻與不分頻。分頻,就是采用baudrate_clock的整數倍頻率采樣;不分頻就是直接global_clock/baudrate_clock,取整,以中間采樣點作為串口電平判決點(可以3點采樣)。前者的誤差范圍可能更小,但是軟件分頻受外界影響大。這里直接采用主時鐘來采樣,探究UART的FPGA/CPLD實現。

通過示波器得出以下結論:

1、串口發送起始位為“0”;

2、串口發送接收位為“1”;

3、數據從高→低位發送;

2、Tx發送設計

下面是接收濾波,同時可以判斷起始位下降沿:

assign neg_rs232_rx = rs232_rx2 ~rs232_rx1;

FIFO數據寄存是接收的主要功能:接收到的直接存高位,移位向低位移動。

begin

if(clk_bps) begin

rx_data_shift = 1'b1;

num = num+1'b1;

if(num=4'd8) rx_temp_data[7] = rs232_rx;

end

else if(rx_data_shift) begin

rx_data_shift = 1'b0;

if(num=4'd8) rx_temp_data = rx_temp_data 》 1'b1;

else if(num==4'd10) begin

num = 4'd0;

rx_data_r = rx_temp_data;

end

end

end

3、Rx接收設計

發送主要考慮到的是接收數據的提取和發送,特別注意的是起始位和結束位的正確賦值。以下是核心代碼:

if(clk_bps) begin

num = num+1'b1;

case (num)

4'd0: rs232_tx_r = 1'b0;

4'd1: rs232_tx_r = tx_data[0];

4'd2: rs232_tx_r = tx_data[1];

4'd3: rs232_tx_r = tx_data[2];

4'd4: rs232_tx_r = tx_data[3];

4'd5: rs232_tx_r = tx_data[4];

4'd6: rs232_tx_r = tx_data[5];

4'd7: rs232_tx_r = tx_data[6];

4'd8: rs232_tx_r = tx_data[7];

4'd9: rs232_tx_r = 1'b1;

default: rs232_tx_r = 1'b1;

endcase

注:重要的幾個問題需要說明一下

1、可以結合自己的時鐘頻率修改clk,而bps_para=clk/baud。

2、另外通過示波器可以發現,結束電平為1bit,那么num=12必須都改為10,這樣可以解決不能發送字符串的問題!

3、發送結束位必須是1,就是高電平,1bit。

評論