IIR數字濾波器設計-在FPGA上實現任意階IIR數字濾波器

IIR數字濾波器的設計

利用MATLAB信號處理工具箱中的濾波器設計和分析工具(EDATool)可以很方便地設計出符合應用要求的未經量化的IIR濾波器。需要將MATLAB設計出的IIR濾波器進一步分解和量化,從而獲得可用FPGA實現的濾波器系數。

由于采用了級聯結構,因此如何將濾波器的每一個極點和零點相組合,從而使得數字濾波器輸出所含的噪聲最小是個十分關鍵的問題。為了產生最優的量化后的IIR數字濾波器,采用如下步驟進行設計:

- 首先計算整體傳遞函數的零極點;

- 選取具有最大幅度的極點以及距離它最近的零點,使用它們組成一個二階基本節的傳遞函數;

- 對于剩下的極點和零點采用與(2)相類似的步驟,直至形成所有的二階基本節。

通過上面三步法進行的設計可以保證IIR數字濾波器中N位乘法器產生的量化舍入誤差最小。 為了設計出可用FPGA實現的數字濾波器,需要對上一步分解獲得的二階基本節的濾波器系數進行量化,即用一個固定的字長加以表示。量化過程中由于存在不同程度的量化誤差,由此會導致濾波器的頻率響應出現偏差,嚴重時會使IIR濾波器的極點移到單位圓之外,系統因而失去穩定性。為了獲得最優的濾波器系數,采用以下步驟進行量化:

- 計算每個系數的絕對值;

- 查找出每個系數絕對值中的最大值;

- 計算比此絕對值大的最小整數;

- 對(3)的結果取反獲得負整數;

- 計算需要表示此整數的最小位數;

- 計算用于表示系數值分數部分的余下位數。

除了系數存在量化誤差,數字濾波器運算過程中有限字長效應也會造成誤差,因此對濾波器中乘法器、加法器及寄存器的數據寬度要也進行合理的設計,以防止產生極限環現象和溢出振蕩。

IIR數字濾波器的VHDL描述

由上一節設計出來的IIR數字濾波器可以進一步用VHDL語言加以描述,通過編譯、功能仿真、綜合和時序仿真之后就可以在FPGA上實現了。由于采用了級聯結構,每一個二階基本節的VHDL描述都是類似的,只是濾波器的系數有所不同,下面著重討論二階基本節的VHDL描述。

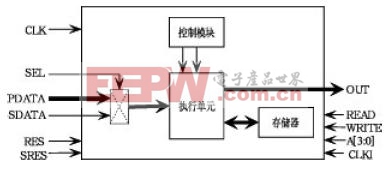

采用VHDL描述的二階基本節的頂層結構如圖3所示。數據在執行單元內進行處理。執行單元內部包含算術和邏輯單元以及一些寄存器;算術和邏輯單元主要由串行乘法器和累加器組成;存儲器包括工作RAM和系數ROM兩部分,分別用于存放計算的中間結果和濾波器的系數;存儲器和執行單元通過內部總線相連接;控制模塊包括程序ROM和程序控制單元,程序ROM中存放有濾波算法的程序,程序控制單元用于解釋指令并為數據處理模塊產生控制信號。

此結構既可以接收串行輸入的數據,也可以接收并行輸入的數據,通過SEL進行設置。外部CPU可以通過READ信號來訪問濾波器的計算結果,另外,外部CPU也可以通過地址總線A[3:0]對內部的存儲器進行訪問,用WRITE信號對濾波器系數進行寫操作,這樣外部CPU就可以根據自己的需要對濾波器進行配置,靈活地實現各種功能。 各信號的含義如下:

- CLK:系統時鐘;

- RES:異步全局復位信號,低有效;

- SDATA:串行輸入數據;

- PDATA:并行輸入數據;

- SEL:設置輸入數據為并行還是串行;

- READ:讀信號,低有效;

- WRITE:寫信號,低有效;

- SRES:同步復位信號,高有效;

- CLKI:外部CPU時鐘;

- A[3:0]:外部CPU訪問內部寄存器的地址總線;

- OUT:輸出數據。

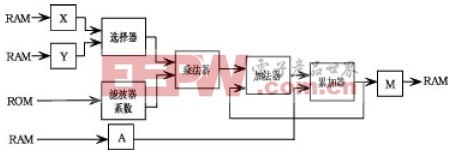

內部算術與邏輯單元是整個濾波器的核心,它的結構如圖4所示。

計算過程是,X、Y為輸入數據,通過選擇器進入乘法器,算術與邏輯單元從系數ROM中讀取濾波器的系數用以輸入數據相乘,相乘的結果與前一步的結果相加進入累加器,累加器讀取上一步計算的中間結果A并計算,最后將此步計算的結果M存入到RAM中去。

結語

本文介紹了一種采用級聯結構在FPGA上實現IIR數字濾波器的方法。在實際使用中,可以根據不同精度要求,方便地對該IIR濾波器進行修改以滿足不同的指標要求,靈活地組成任意階不同類型的濾波器。同時,在系統運行中,外部CPU可以靈活修改濾波器系數,改變濾波器的頻率響應,滿足特定的應用要求。

評論