一種應用于OFDM系統中的符號精確定時算法的FPGA實現

圖5是采用判決函數取近似值的Matlab仿真圖,圖6是判決函數取確定值的Matlab仿真圖。檢測峰值時,第一個峰值是由于循環前綴存在的影響,峰值檢測時檢測第二個峰值。從圖5,圖6中可以看出,在判決函數近似處理雖然會損耗算法的性能,但是判決函數仍然存在明顯峰值,選擇適當的閾值時,仍然可以精確定時同步,可見減少對判決函數的近似對性能并未造成很大的影響。

表1是在AWGN環境下精同步位置的仿真結果,每個信噪比下經過5 000幀的仿真。符號同步偏差表示每個信噪比下的精同步平均錯誤長度,可見在系統的性能并未明顯降低。

3.2 精同步模塊實際實現

硬件設計是基于XLINX公司的SPRTAN6系列中的XC6SLX150-2FGG484芯片,采用Verilog HDL語言,仿真軟件是ISE自帶的ISIM,開發環境是ISE。

整個OFDM系統同步的ISIM仿真波形如圖7所示。其中:clk_i表示時鐘信號;reset_i表示同步復位信號;clk5M_en_i表示5 MHz時鐘使能信號;nrst_j表示異步復位信號;acq_val_o表示粗捕獲指示信號;dataI_o,dataQ_o表示經過粗捕獲和粗頻偏估計的輸出信號;

sync_val_o表示精同步指示信號。

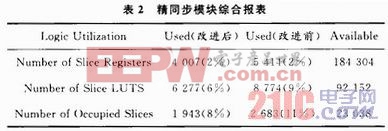

經過ISE綜合后,改進前和改進后精同步占用資源分布如表2所示。

由表2可見本文對系統資源優化的效果十分明顯。

4 結語

本文分析了一種OFDM系統精同步算法的原理,給出了FPGA硬件實現方案和結果分析,該方案在采用經典算法的同時,對算法進行了改進,在不降低精同步性能的前提下大大降低了計算復雜度,并且設計結構簡單,易于實現,具有較好的工程實用價值。

評論