FPGA為設計平臺的全彩led顯示屏設計方案

作為一個獨立的顯示系統,普通的RS232 、RS485 總線方式已不能滿足L ED 顯示屏進行多媒體視頻播放所要達到的高數據速率傳輸要求。以512 ×256 的全彩顯示屏為例,當要求系統換幀頻率達到30 Hz 時,需要的數據傳輸速率高達94. 4 Mbp s。因此,在系統設計中,視頻數據的傳輸和接收采用RTL8201 設計的100 M 以太網控制器來完成。

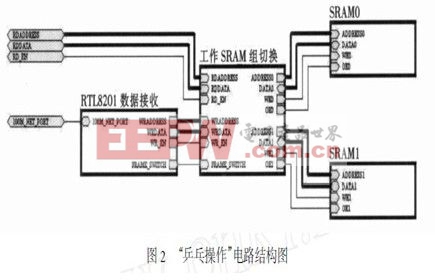

為了使視頻播放連續平滑,在數據接收過程中不能打斷顯示,這里采用兩組SRAM 進行“乒乓操作”,使顯示數據的接收存儲和讀取能夠同時進行, 從而實現視頻數據流的無縫緩沖和處理 , 如圖2 所示。換幀信號FRAME _SWITCH 是用來切換工作SRAM 組的,該信號決定兩組SRAM 哪一組處于讀狀態,哪一組處于寫入狀態。RTL8201 數據接收模塊建立MII 接口,實現與RTL8201 的接口,把MII 接口傳送過來的半字節數據轉換成為24 位RGB 數據,然后存儲在SRAM 里。RTL8201 每接收完一幀顯示數據,則對換幀信號FRAME_ SWITCH 進行求反,將兩組SRAM 的讀寫位置切換過來,使顯示屏顯示最新接收到的幀數據,從而實現換幀操作。

由于LED 顯示屏包含4 列相互獨立的顯示模塊,因此掃描控制電路需要提供4 路RGB 數據輸出接口, 在圖1 中表示為RGB0 ~ RGB3 。

CLOCK_OUT 為移位時鐘信號輸出端口,RGB0~RGB3 在該時鐘的上升沿有效,各個端口的紅、綠、藍三色顯示數據通過時鐘脈沖信號分別逐位移入驅動芯片的顯示緩存。LA TCH 信號為串行數據輸出結束后需要進行顯示刷新時的鎖存脈沖。EN 為灰度控制信號,當EN 有效時,L ED 可以隨輸入數據的0 、1 狀態熄滅或者點亮,其有效時間寬度對應為表2 所示的點亮時間。

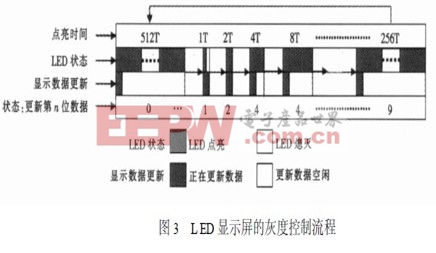

EN 信號產生模塊為實現灰度圖像顯示的重要模塊,該模塊將輸入的位計數值轉換成為對應位的點亮時間,并進行相應時間長度的亮度控制。

在本設計中,輸入的灰度信號為256 級,考慮到反γ非線性校正過程引起的灰度損失,將輸出的灰度級別定義為1 024 級,因此需要得到10 位灰度數據各個位對應的點亮時間。依據“灰度實現原理”,10 位灰度數據各個數據位對應的點亮時間從D0 ~D9 分別從1 T 倍增為512 T ,點亮總時間為1 023 T 。

由于驅動板中驅動芯片有二級緩存功能,所以更新數據和點亮L ED 這兩個控制過程可以部分重疊,從而得到圖3 所示的LED顯示屏灰度控制流程。更新第0 位數據時點亮時間為512 T 、更新第1 位數據時點亮時間為1 T ...依次類推,更新第n 位數據時,控制點亮的時間為上一次所更新的位所需要的點亮時間。

4、結論

討論了一種大屏幕全彩LED 顯示屏設計的掃描控制器設計方案,通過對“19 場掃描”實現方法的分析,針對其不足之處,提出了一種新式的逐位點亮灰度控制方法。該控制方法使得在全彩LED 顯示屏的設計中,可以在L ED 的發光效率和刷新率之間進行靈活的調整。本設計采用FP2GA 控制芯片為設計平臺來完成掃描控制電路的實現,借助EDA 開發工具,降低了驅動電路的設計難度,縮短了項目的開發周期。

評論