從4004到core i7——處理器的進(jìn)化史-CPU構(gòu)成零件-2

在上一個(gè)帖子當(dāng)中我們見(jiàn)到了MOS管。下面我們來(lái)看一看用它完成的一個(gè)最簡(jiǎn)單的設(shè)計(jì)。

本文引用地址:http://www.104case.com/article/221713.htm

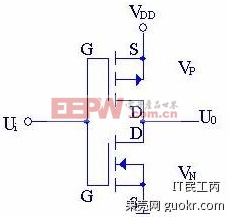

看看上面這個(gè)電路。一只PMOS管和一只NMOS管串聯(lián)起來(lái),共享門極輸入和漏極輸出。這樣的電路,即PMOS在上,NMOS在下被稱為互補(bǔ)MOS工藝,Complementary MOS,簡(jiǎn)稱CMOS。在上面的圖片中使用的符號(hào),S與D中間的箭頭表示的是當(dāng)這個(gè)類型的MOS管導(dǎo)通時(shí)底襯中的電子究竟是被吸引在底襯表面還是被排斥出底襯表面。

下面簡(jiǎn)要的分析一下:

Ui->VDD NMOS 導(dǎo)通 Uo->0 (Pull-down)

Ui->0 PMOS 導(dǎo)通 Uo->VDD (Pull-up)

也就是說(shuō),我們僅僅用兩只管子就構(gòu)成了一個(gè)可以將輸入信號(hào)的電平反轉(zhuǎn)的電路。

這個(gè)電路叫做反相器。許多經(jīng)典的教科書在教授數(shù)字邏輯時(shí)都以它為例,我們也不例外。

進(jìn)一步分析,我們發(fā)現(xiàn)這個(gè)反相器具有2個(gè)優(yōu)良的特性。

由于NMOS管的Source接在地上,所以當(dāng)Ui=VDD時(shí)NMOS保證導(dǎo)通,它可以將Uo的電平一直拉到地上;

由于PMOS管的Source接在VDD上,所以當(dāng)Ui=0是PMOS保證導(dǎo)通,他可以將Uo的電平一直拉到VDD。

更重要的是,只要是NMOS管和PMOS管組合起來(lái)就可以保證上面所說(shuō)的輸出電平水平,而PMOS和NMOS的具體參數(shù)(比如說(shuō),溝道長(zhǎng)寬比)不會(huì)產(chǎn)生影響。也就是說(shuō),我們得到了比例無(wú)關(guān)的邏輯。這是個(gè)非常棒的特性。

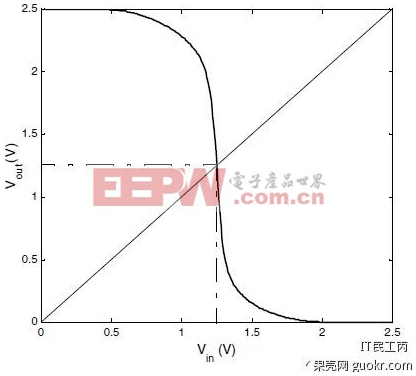

我們?cè)賮?lái)考慮反相器的電壓傳輸特性。顯然,上面關(guān)于電平值的分析是不完整的,因?yàn)楫?dāng)輸入連續(xù)變化時(shí)輸出不可能跳變。看看下面這張圖片:

可以看到,CMOS反相器的電壓傳輸特性曲線中間部分非常陡峭。我們把Vout=Vin的點(diǎn)叫做反相器的閾值電壓。CMOS反相器的特性是,在閾值電壓附近輸出迅速完成了電平的切換,而在其他區(qū)域輸出電平幾乎不變。

數(shù)字電路的核心思想在于以電平表示邏輯。如果我們定義2~2.5V為‘1’,0~0.5V為‘0’,我們吃驚地發(fā)現(xiàn)當(dāng)在輸入為0~1.1V以及1.4V~2.5V時(shí)輸出電平全都落在我們的定義范圍內(nèi),全部都是有意義的!也就是說(shuō),CMOS具有高噪聲容限。如果我們將輸入的電平相對(duì)于0、VDD這一對(duì)“標(biāo)準(zhǔn)邏輯電平”的誤差,那么我們發(fā)現(xiàn)CMOS反相器可以壓縮誤差!

比例無(wú)關(guān)邏輯、高噪聲容限、壓縮誤差,還有后文中提到的靜態(tài)邏輯,這一切僅僅需要簡(jiǎn)單地NMOS+PMOS就可以實(shí)現(xiàn),你也許看出為什么現(xiàn)代的集成電路選擇CMOS工藝了吧?

DIY機(jī)械鍵盤相關(guān)社區(qū):機(jī)械鍵盤DIY

評(píng)論