一種通用數據采集系統的設計方案

2 硬件設計

本文引用地址:http://www.104case.com/article/221483.htm以前端接口板a的實現為例,其主要構成為16位的D/A轉換器DAC7731模塊、14位A/D轉換器TLC3574模塊及其他輔助電路。

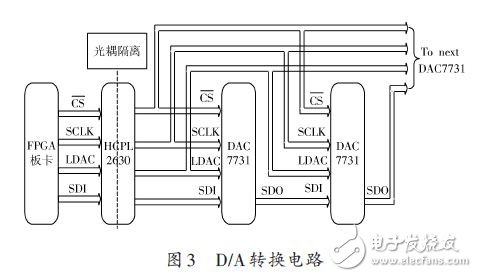

2.1 D/A轉換電路

DAC7731 為16 位的數字模擬轉換芯片,其內部提供+10 V 的參考電壓。將其模擬量輸出通過引腳設置為-10~+10 V 的電壓范圍。DAC7731 具有帶雙緩沖的標準三線SPI串行接口,允許模擬輸出的異步更新。如圖3 所示,它還有一個串行數據輸出線以實現多片DAC7731的鏈接。系統工作時由LabVIEW圖形化編程開發平臺通過FPGA生成和發送DAC7731芯片的SPI接口和時序控制信號,通過SDI信號依次將需要轉換的數據以從最后一片到第一片的順序發送給每片DAC7731,之后通過C-S 和LADC 信號實現多片DAC7731的同步轉換輸出。

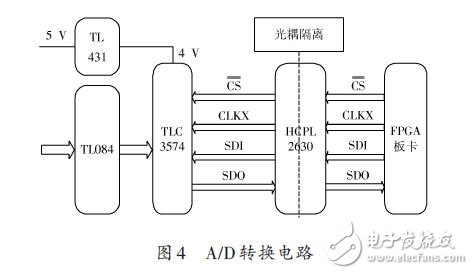

2.2 A/D轉換電路

綜合考慮系統的分辨率、通道數、采樣率、采樣范圍和接口等要求,系統的ADC 選用TI公司的14位8通道高性能逐次逼近型模數轉換器TLC3574.該器件工作頻率高達25 MHz,采用偽差分的模擬輸入電路,將采樣信號的動態范圍擴展為±10 V,其內含的采樣和保持功能使得外圍電路大為簡化。在輸出接口上,該器件采用SPI/DSP兼容的串行接口方式,從而極大地減少了接口的連線數量。A/D 轉換電路原理如圖4 所示,由FPGA生成TLC3574的SPI接口和時序信號,控制其將外部的模擬信號轉換后輸入到FPGA,進行相應的計算和處理。由于TLC3574 片內沒有電壓基準,可選用TI 公司的三端可調分流基準源TL431組成外圍電路為其提供一個高精度的4 V電壓基準。

考慮到信號的阻抗匹配需要,ADC 的輸入前端需要有一個緩沖運放,其性能必須與ADC的性能相匹配,否則會影響和限制ADC的性能。在數據采集過程中如果信號的變化幅度比較大,則需要根據信號的變化相應調整放大器的增益。否則,單一的增益放大會使得放大后的信號幅值很有可能超過ADC的轉換量程。這里所采集的信號其變化幅度不是很大,采用TI公司高轉換率的輸入端運算放大器TL084就可以滿足系統的使用要求。

2.3 數字量輸入/輸出設計

直接將通用背板的FPGA端口引到前端接口板,根據測試對象的接口電路,如27 V/開、地/開等形式,選擇繼電器、OC門、光耦隔離等方式,實現數字量的輸入和輸出。

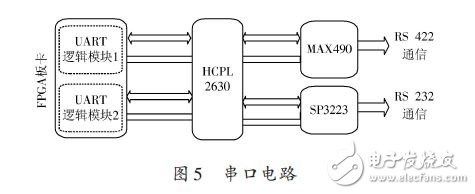

2.4 串口電路設計

由于FPGA板卡具有便利的輸入輸出控制功能,利用FPGA 板卡可以很方便的通過連接不同的接口芯片選擇相應的串口模式。MAX490是低功耗收發器,用于RS 485 與RS 422通信。它具有一個驅動器和一個接收器,驅動器擺率不受限制,可以實現最高2.5 Mb/s的傳輸速率。驅動器具有短路電流限制,并可以通過熱關斷電路將驅動器輸出置為高阻狀態,防止過度的功率損耗。接收器輸入具有失效保護特性,當輸入開路時,可以確保邏輯高電平輸出。如圖5所示,通過連接低功耗收發器MAX490可以實現RS 422通信,而改接SP3223芯片后就可以實現RS 232通信,區別只是在于FPGA中建立的UART邏輯模塊有所不同,進一步顯示了系統良好的通用性。

光耦相關文章:光耦原理

評論