基于ADS1298與FPGA的高性能腦電信號采集系統(tǒng)

3 軟件模塊設計

本文引用地址:http://www.104case.com/article/221427.htm3.1 FPGA內(nèi)部信號處理控制模塊設計

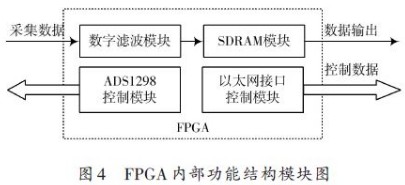

本系統(tǒng)使用Verilog HDL語言單獨編寫A/D轉換器的控制模塊、SDRAM存儲器控制模塊、數(shù)字濾波器模塊以及以太網(wǎng)端口傳輸控制模塊,通過功能仿真和時序仿真來驗證各個模塊是否能夠獨立完成相對應的控制功能。驗證成功后,最終通過例化,在FPGA內(nèi)部形成一個腦電信號采集系統(tǒng)的核心處理控制模塊,圖4為核心處理控制模塊的具體功能結構模塊框圖。

3.2 ADS1298軟件設計

本系統(tǒng)中最重要的一環(huán)就是模/數(shù)轉換,這里重點介紹ADS1298的軟件模塊設計。ADS1298的工作流程主要包括:上電初始化、發(fā)送操作命令和配置寄存器、開始轉換并讀取轉換數(shù)據(jù)。ADS1298的操作命令主要分為數(shù)據(jù)操作命令和寄存器讀寫命令。數(shù)據(jù)操作命令主要包含SDATA和RDATAC(連續(xù)讀數(shù)據(jù))。連續(xù)讀數(shù)據(jù)只需要寫入一次RDATAC 操作命令,就可以在每次的DRDY變?yōu)榈碗娖綍r讀取轉換數(shù)據(jù)。寄存器讀寫命令分為RREG 和WREG.這兩個操作命令分別包含兩個字節(jié),第一個字節(jié)為讀寫寄存器的起始地址,第二個字節(jié)為讀寫寄存器的個數(shù)。

FPGA 軟件編程中具體的ADS1298 模塊內(nèi)部框圖如圖5所示。

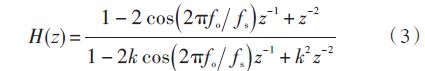

3.3 數(shù)字濾波模塊軟件設計

本系統(tǒng)的數(shù)字濾波模塊主要為50 Hz 陷波器和數(shù)字帶通濾波器,兩者的軟件設計方法相似,這里重點介紹50 Hz 的陷波器設計方法。本系統(tǒng)中設計的陷波器技術指標為:抽樣頻率fs 為1 kHz,陷波頻率fo 為50 Hz,3 dB 帶邊頻率為45 Hz和55 Hz,阻帶上下邊頻率為49 Hz和51 Hz,阻帶衰減不小于40 dB.為了便于硬件的實現(xiàn),本文選用二階的IIR 陷波器,其傳遞函數(shù)如式(3)所示:

k 的值決定了陷波深度,根據(jù)具體的信號進行調整,從而實現(xiàn)最佳陷波。對于EEG信號,最佳的k 取值為0.88.FPGA軟件設計時需要根據(jù)傳遞函數(shù)設置幾個寄存器存儲系數(shù)和中間值,并在每個時鐘對這些中間值移位更新,然后重新計算得到新的輸出值。

4 結語

系統(tǒng)采用Altera Cyclone Ⅱ系列芯片EP2C35F672作為控制和處理的核心,8通道、低噪聲、低功耗、24位的Σ-△模/數(shù)轉換芯片ADS1298作為采集系統(tǒng)核心,簡化了系統(tǒng)的硬件設計,具有功耗低、便攜式、精度高等優(yōu)點;采用FPGA和DM9000A以太網(wǎng)控制器相結合,成功的將腦電信號采集系統(tǒng)和PC上位機相連,避免了直接上傳時的數(shù)據(jù)丟失,實現(xiàn)了彼此間的高速數(shù)據(jù)通信。本系統(tǒng)利用Quartus Ⅱ工具和Verilog HDL 語言對FPGA進行設計、仿真和驗證,便于設計的修改和優(yōu)化,大大縮短了產(chǎn)品的開發(fā)設計周期,因此本系統(tǒng)具有良好的使用價值和應用前景。

模擬信號相關文章:什么是模擬信號

fpga相關文章:fpga是什么

模數(shù)轉換器相關文章:模數(shù)轉換器工作原理

評論