基于ARM+FPGA+多DSP的嵌入式實(shí)時(shí)圖像處理系統(tǒng)

在本系統(tǒng)中,F(xiàn)PGA內(nèi)部需要設(shè)計(jì)一邏輯時(shí)序完成圖像數(shù)據(jù)的采集,數(shù)據(jù)的傳輸采用異步FIFO完成。采用此方案可以解決CCD輸出數(shù)據(jù)頻率與從DSP和ARM不匹配的問(wèn)題。

4 DSP的EMIFA與FPGA實(shí)現(xiàn)的軟FIFO接口

4.1 DSP的EMIFA接口[4-5]

DSP(TMS320DM6416T)之間的通信都是通過(guò)外部存儲(chǔ)器接口(EMIFA)訪問(wèn)片外存儲(chǔ)器進(jìn)行的。EMIFA由64 bit數(shù)據(jù)線D[63:0]、20 bit地址線A [22:03]、 8 bit字節(jié)使能線BE[7:0]、4 bit地址區(qū)域片選線/CE3~/CE0和各類存儲(chǔ)器的讀/寫控制信號(hào)組成。TMS320DM6416T 的每個(gè)

/CEx空間都有256 MB尋址空間,并且可配置為與SRAM、SDRAM、ZBTSRAM、Flash、FIFO等各類存儲(chǔ)器接口。EMIFA讀/寫各類存儲(chǔ)器的時(shí)鐘可由軟件配置為EMIF的AECLKIN、CPU/4或CPU/6。本設(shè)計(jì)配置為EMIF的AECLKIN,且為133 MHz。

4.2 EMIF與軟FIFO接口實(shí)現(xiàn)

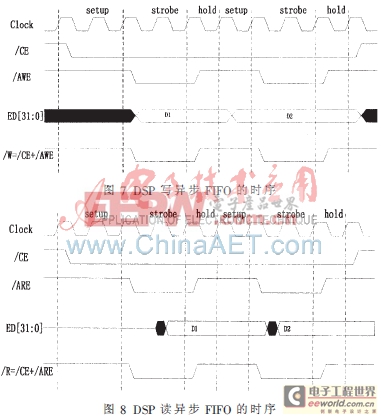

DSP之間通過(guò)EMIF口與FPGA實(shí)現(xiàn)的異步FIFO進(jìn)行通信。EMIF異步接口的每個(gè)讀/寫周期分為三個(gè)階段:建立時(shí)間(SETUP)、觸發(fā)時(shí)間(STROBE)、保持時(shí)間(HOLD),且每個(gè)階段時(shí)間可編程設(shè)置,以適應(yīng)不同的讀寫速度。DSP讀寫異步FIFO的時(shí)序圖分別如圖7、圖8所示[6]。DSP讀寫FIFO控制信號(hào)由FPGA產(chǎn)生,其邏輯關(guān)系如下:

寫FIFO信號(hào):writ_clk= AECLKOUT

writ_req=! (/CE+/AWE)

讀FIFO信號(hào):read_clk = AECLKOUT

read_req = ! (/CE+/ARE)

另外,寫FIFO的DSP要相應(yīng)為滿狀態(tài)標(biāo)志,讀FIFO的DSP則相應(yīng)為半滿狀態(tài)標(biāo)志。

5 DSP之間數(shù)據(jù)通信[7]

為了設(shè)計(jì)一款通用性比較強(qiáng)的圖像處理平臺(tái),各處理器間的數(shù)據(jù)傳輸必需達(dá)到通用性,這樣可以針對(duì)不同系統(tǒng)的應(yīng)用,只須修改圖像處理算法代碼,而不須要修改各處理器之間的通信。具體設(shè)計(jì)分為如下兩部分:

(1) 數(shù)據(jù)通信協(xié)議說(shuō)明(x=0,1,2,3)

Se/Re (Send/Receive)[0]:ARM通過(guò)FPGA請(qǐng)求DSPx接收(該數(shù)據(jù)位為1)或發(fā)送。

ARM[1:3]:該段數(shù)據(jù)為DSPx向FPGA發(fā)出請(qǐng)求數(shù)的DSP編號(hào)。

DSPx[4:6]:ARM處理器向FPGA提出要求響應(yīng)的DSP的編號(hào)。

Da_Le(Data_Leng)[7:18]:ARM請(qǐng)求DSPx接收或發(fā)送的數(shù)據(jù)長(zhǎng)度。

Da_Un (Data_Unit)[19]:該標(biāo)志位表示是否按照Data_leng*K(1K=1 024 bit)的數(shù)據(jù)長(zhǎng)度傳輸數(shù)據(jù),若為1,表示接收或發(fā)送數(shù)據(jù)長(zhǎng)度為Data_leng*K(1K=1024 bit);若為0,表示接收或發(fā)送數(shù)據(jù)長(zhǎng)度為Data_leng。

Da_Bl (Data_Block)[20:27]:該數(shù)據(jù)表示ARM請(qǐng)求DSPx接收或發(fā)送Data_Block個(gè)Data_leng K或Data_leng數(shù)據(jù)塊。

Da_Ch(Data _Result)[7:18]:ARM請(qǐng)求DSPx接收或發(fā)送的算法代碼中間運(yùn)行結(jié)果或最終結(jié)果,此數(shù)據(jù)段與Data_Leng共用。

In_Pr (Interrupt _Priority) [27:30]:設(shè)置DSP的中斷優(yōu)先權(quán)。

Ot_Use (DSP_State) [31:34]:DSP狀態(tài)標(biāo)志信息。

Ot_Use (Other_Use) [36:47]:用戶自定義數(shù)據(jù)段。

(2) 數(shù)據(jù)通信主要流程

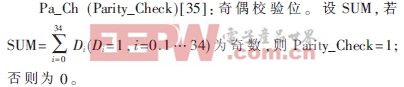

首先,F(xiàn)PGA接收到ARM[1:3]處理器的請(qǐng)求信號(hào),然后根據(jù)Data[0:34]計(jì)算出校驗(yàn)數(shù)據(jù)SUM與Parity_Check[35]比較,若不等,則FPGA向ARM處理器重新發(fā)請(qǐng)求信號(hào);若相等、且DSPx為空閑狀態(tài)時(shí),則FPGA由Send/Receive向DSPx發(fā)送接收或發(fā)送數(shù)據(jù)請(qǐng)求,并將采集到的圖像數(shù)據(jù)傳輸給DSPx,同時(shí)使能對(duì)應(yīng)的FIFO數(shù)據(jù)通道;DSPx根據(jù)收到的數(shù)據(jù)信息,同樣計(jì)算出校驗(yàn)數(shù)據(jù),若與Parity_Check相等,則根據(jù)Send/Receive標(biāo)志位,采用EDMA方式向EMIF口接收或發(fā)送Data_Block* Data_leng(或Data_Block* Data_leng K)數(shù)據(jù)。如果FPGA同時(shí)接收到2個(gè)或2個(gè)以上的DSPx數(shù)據(jù)傳輸請(qǐng)求信號(hào),則FPGA根據(jù)Interrupt _Priority端口數(shù)據(jù)判其執(zhí)行的先后順序。

6 系統(tǒng)的性能分析[7]

影響系統(tǒng)性能的主要因素有:ARM處理器協(xié)調(diào)工作的響應(yīng)速度、DSP處理數(shù)據(jù)的速度、數(shù)據(jù)在多處理器之間的傳輸速度。前兩個(gè)因素主要由處理的主頻和處理能力決定,因此不做測(cè)試。數(shù)據(jù)在處理器之間的傳輸速度則是本設(shè)計(jì)的主要部分之一,而數(shù)據(jù)傳輸帶寬和數(shù)據(jù)傳輸延遲是衡量數(shù)據(jù)傳輸速度的重要指標(biāo)。

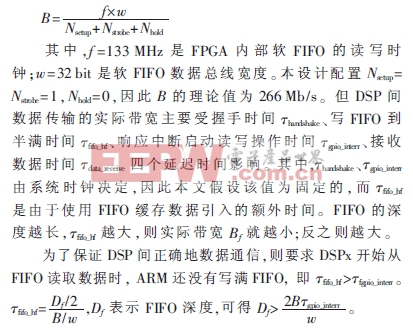

若系統(tǒng)中DSP讀寫FIFO的帶寬為B(單位時(shí)間內(nèi)DSP間的數(shù)據(jù)傳輸量),則:

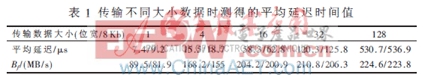

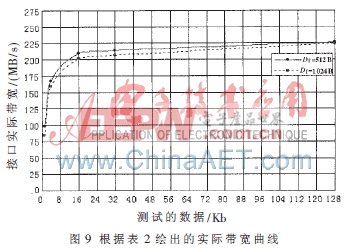

表1是ARM處理器分別與DSP1~DSP4傳輸不同大小數(shù)據(jù)時(shí)測(cè)得的平均延遲時(shí)間,圖9是根據(jù)測(cè)試數(shù)據(jù)繪出的實(shí)際帶寬Bf曲線。可以看出,隨著傳輸?shù)臄?shù)據(jù)增大,Bf逐漸逼近B的266 MB/s的理論值。

本文基于ARM、FPGA、多DSP設(shè)計(jì)的實(shí)時(shí)圖像信號(hào)處理系統(tǒng),使用FPGA芯片設(shè)計(jì)的一種高速數(shù)據(jù)傳輸網(wǎng)絡(luò)互聯(lián)結(jié)構(gòu),使得該系統(tǒng)的數(shù)據(jù)通信能力和DSP的運(yùn)算能力能很好地匹配;通過(guò)數(shù)據(jù)傳輸控制總線,使得數(shù)據(jù)傳輸十分靈活;利用S3C6410對(duì)圖像數(shù)據(jù)傳輸?shù)恼{(diào)度,圖像數(shù)據(jù)處理任務(wù)的分配,圖像保存、顯示、網(wǎng)絡(luò)傳輸;利用4個(gè)TMS320C6416T對(duì)圖像做算法處理。經(jīng)測(cè)試,算法代碼在單DSP(TMS320C6416T 1 GHz)平臺(tái)下其處理時(shí)間小于0.2 s,而在本文平臺(tái)下其處理時(shí)間小于40 ms,可以滿足實(shí)時(shí)要求。另外,該系統(tǒng)可廣泛適用于其他圖像處理、電子對(duì)抗、雷達(dá)信號(hào)處理等各個(gè)領(lǐng)域。

參考文獻(xiàn)

[1] 曹理發(fā).尹勇.劉恒輝,等.基于ARM和DSP的視頻監(jiān)控系統(tǒng)設(shè)計(jì)與實(shí)現(xiàn)[J].電子器件,2009,32(1).

[2] Cyclonce Inc. Cyclone II device handbook. 2005.

[3] 龍?jiān)俅ǎw凱生,洪明堅(jiān),等. ARM系統(tǒng)中DMA方式在數(shù)據(jù)采集中的應(yīng)用[J].國(guó)外電子元器件,2007(2).

[4] Texas Instruments Incorporated.TMS320C6414,TMS320C6415, TMS320C6416FIXED-Point digital signal processor,2007.

[5] 李方慧,王飛,何佩琨. TMS320C6000系列DSPs原理與應(yīng)用(第二版)[M].北京:電子工業(yè)出版社,2005.

[6] Texas Instruments Incorporated. TMS320C6000 EMIF to external FIFO interface.1999.

[7] 周委,陳思平,趙文龍,等. 基于DSP EMIF口、FPGA設(shè)計(jì)并實(shí)現(xiàn)的多DSP 嵌入式系統(tǒng)[J]. 電子技術(shù)應(yīng)用, 2008,34(12):6-8.

評(píng)論