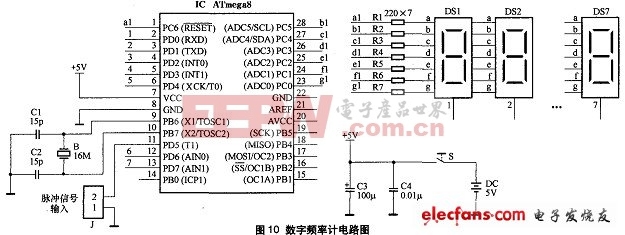

基于51單片機和CPLD的數字頻率計的設計

引言

在傳統的控制系統中,通常將單片機作為控制核心并輔以相應的元器件構成一個整體。但這種方法硬件連線復雜、可靠性差,且在實際應用中往往需要外加擴展芯片,這無疑會增大控制系統的體積,還會增加引入干擾的可能性。對一些體積小的控制系統,要求以盡可能小的器件體積實現盡可能復雜的控制功能,直接應用單片機及其擴展芯片就難以達到所期望的效果。

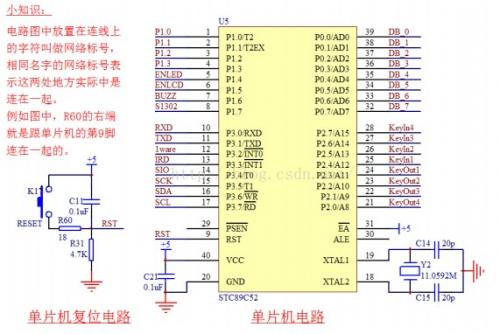

復雜可編程邏輯器件(CPLD)具有集成度高、運算速度快、開發周期短等特點,它的出現,改變了數字電路的設計方法、增強了設計的靈活性。基于此,本文提出了一種采用Altera公司的CPLD(ATF1508AS) 和Atmel公司的單片機(AT89S52)相結合的數字頻率計的設計方法。該數字頻率計電路簡潔,軟件潛力得到充分挖掘,低頻段測量精度高,有效防止了干擾的侵入。獨到之處體現在用軟件取代了硬件。

CPLD開發環境簡介

1 VHDL語言

VHDL(Very High Speed Integrated Circuit Hardware Description Language,超高速集成電路硬件描述語言)是由美國國防部開發的一種快速設計電路的工具,目前已經成為IEEE的一種工業標準硬件描述語言。相比傳統的電路系統設計方法,VHDL具有多層次描述系統硬件功能的能力,支持自頂向下和基于庫的設計的特點,因此設計者可以不必了解硬件結構。從系統設計入手,在頂層進行系統方框圖的劃分和結構設計,在方框圖一級用VHDL對電路的行為進行描述,并進行仿真和糾錯,然后在系統一級進行驗證,最后再用邏輯綜合優化工具生成具體的門級邏輯電路的網表,下載到具體的CPLD器件中去,從而實現可編程的專用集成電路(ASIC)的設計。

2 Max+PlusⅡ開發工具

Max+PlusⅡ開發工具是美國Altera公司自行設計的一種CAE軟件工具。它具有全面的邏輯設計能力,設計者可以自由組合文本、圖形和波形輸入法,建立起層次化的單器件或多器件設計。利用該工具配備的編輯、編譯、仿真、綜合、芯片編程等功能,將設計的電路圖或電路描述程序變成基本的邏輯單元寫入到可編程芯片中(如CPLD、FPGA),做成ASIC芯片。

它支持FLEX、MAX及Classic等系列CPLD器件,設計者無須精通器件內部的復雜結構 ,只需用自己熟悉的設計輸入工具,如高級行為語言、原理圖或波形圖進行設計輸入,它便將這些設計轉換成目標結構所要求的格式,從而簡化了設計過程。而且 Max+PlusⅡ提供了豐富的邏輯功能庫供設計者使用。設計者利用以上這些庫及自己添加的宏功能模塊,可大大減輕設計的工作量。使用Max+PlusⅡ 設計CPLD器件的流程如圖1所示。

圖1 Max+PlusⅡ設計CPLD器件的流程圖

評論