電子電路設計之C51單片機常見問題

3:51單片機的P0口特殊之處

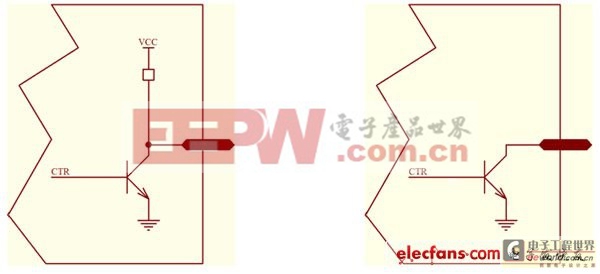

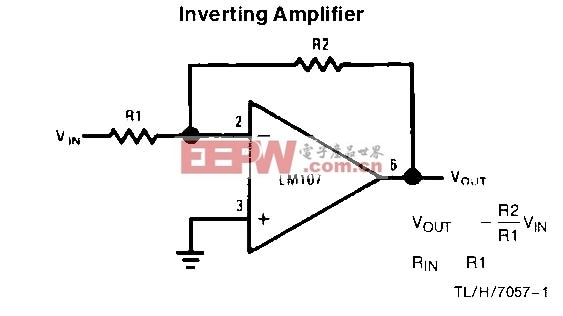

許多新手都碰到這個問題,其實很簡單,這涉及到芯片的io腳是怎么做出來的。這對硬件工程師來說十分重要。TTL的io腳模型:

P1,P2,P3口都可以理解成左圖,注意vcc下面有個電阻,因此可以理解成:引腳輸出1的能力弱。地那邊沒有電阻,可以理解成引腳吸入電流能力強。而P0口,可以理解成右圖。這就是集電極開路輸出,也叫OC輸出。可以看出,當CTR=1時,三極管導通,引腳被接地;當ctr=0時,三極管截止,引腳浮空,也叫三態。這個端口這么做的目的是考慮P0口肩負讀寫數據和地址復用,這個關系要仔細看懂cpu時序圖。因此,P0口要加合適的上拉電阻,絕不要加下拉電阻。上拉電阻的選擇要看外部負載情況。

4:P1-3口如何輸入輸出

從上節的左圖可以看出。做輸出時,ctr=1則輸出強信號0,ctr=0則輸出弱信號1。當io腳做輸入時,應使ctr=0,這樣三極管截止。外部信號如果是1,則上拉電阻加強了這個1,單片機就會讀到1。當外部信號為0時,注意,必須將上拉電阻的上拉作用全部抵消,才能在引腳上得到0。

因此,對于程序來說,把io腳置1就處于接收狀態,當然也是輸出1狀態。程序置io口為1,讀取的信號是不是1就依靠外部電路了,如果外部電路沒有“吃掉”上拉電阻的電流,則讀取得到1,反之,雖然程序置io腳為1,但是讀取得到的就是0。

因此,如果用io腳的高電平驅動外部電路時,要小心外部電路把這個1“吃掉”從而輸出不了1。而作為輸入時,為0電平的外設必須足夠有能力將io腳拉低。所以,用io腳直接點亮led的時候,最好用反邏輯,就是輸出0,讓led亮。這樣能保證驅動能力。就是io腳接led的負端,led的正端過電阻接vcc。

因此,io腳輸出1時,外部電路將它強行接地是沒有關系的,而io腳輸出0的時候,外部電路強行接電源就會把io腳損壞。所以,程序加電之后,一般把所有io口都寫成1:MOV P0,0FFH。

P3口引腳復用,必須引腳都處于輸出1狀態。例如,把RXD腳輸出0,則它什么數據都讀不進來了,筆者早期曾調試一整天才發現串口收不到數據是沒有把RXD置1的原因,把時間都浪費在外圍了,當時很是汗顏。

5:有關晶振

單片機的晶振在內部可以簡化成一個反向器。當晶振輸入腳XI剛過坎壓、被認為是1的一瞬間,輸出腳XO就輸出0,這個0會帶動晶振使XI電壓下降,當降低到坎壓被認為是0的一瞬間,輸出腳XO就輸出1。這樣周而復始。

因此,用示波器觀察正常工作的晶振輸入腳XI時,得到的是一個不高不低的近似水平線。而XO則是幅值很大的正弦波。測量晶振輸入腳XI時,示波器表筆要打在X10檔上,否則,表筆就能把晶振弄停。

因此布線時,晶振輸入腳XI要盡量靠近晶振,而XO腳可稍遠。同時XO具有一定的驅動能力,某些芯片可以用它驅動其它時序電路(不推薦這么做,因為系統可靠性下降)。

寫到這里,才發覺51單片機的問題太多了,這篇文字簡直就是滄海一粟。以后再補充吧,另行成文。

評論