基于51單片機IP核的FPGA實現與應用

1 引言

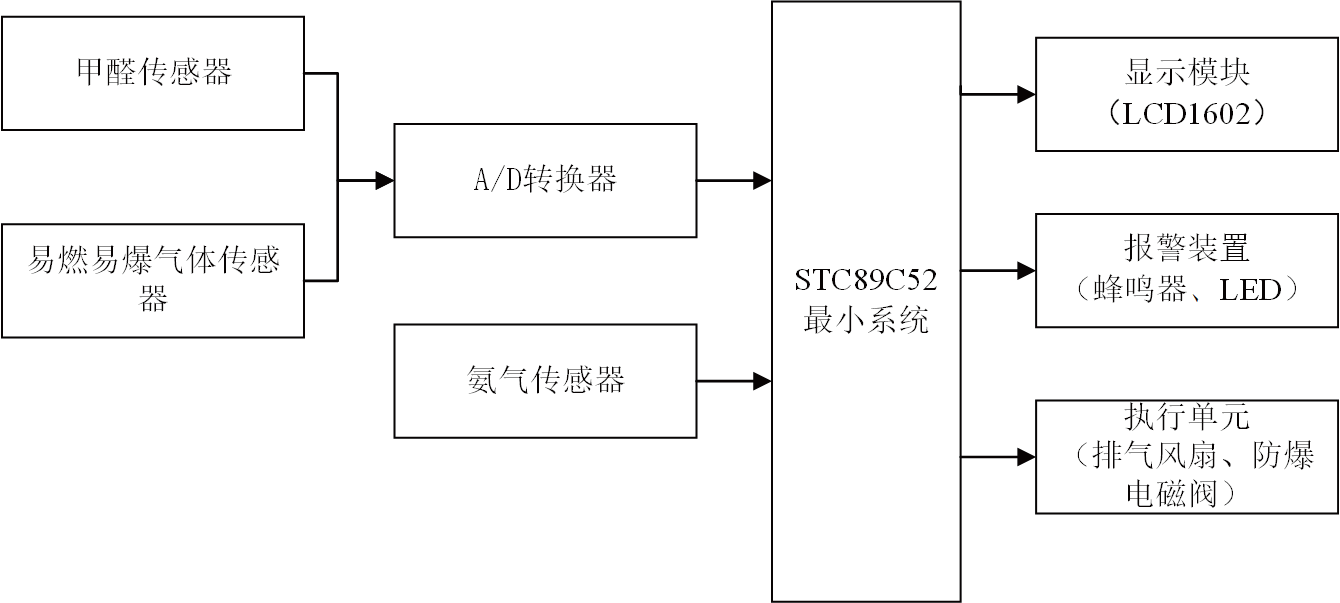

長期以來,單片機以其性價比高、體積小、功能靈活等方面的獨特優點被廣泛應用。但受其內部資源的限制,單片機需要在片外擴展相關資源。為了達到處理速度和控制靈活性方面的需求,采用微控制器和可編程邏輯器件設計單片機嵌入式系統。隨著現場可編程邏輯陣列(FPGA)及EDA技術的發展,百萬門級的FPGA、可重構的嵌入式MCU核、功能復雜的IP核及各種功能強大的EDA工具的出現,實現將MCU、存儲器和一些外圍電路集成到一個芯片成為可能。隨著IP核技術在FPCA中的應用,特別是MCU IP核技術的發展。出現了性能不同的嵌入式MCU軟核。MCS-51系列MCU是目前應用時間最長、最普及、可獲得應用資料最多的功能強大的8位MCU,建立805l MCU可綜合IP核對于各種嵌入式系統和片上系統(SOC)的應用。針對8051MCU的應用前景,出現了幾個比較典型的805l IP核,如DW8051核.OpenCore組織的0C8051核及T51核,MC805l核等。這些IP核都是采用HDL語言描述的軟MCU內核,其與工藝無關,能夠在多種FPGA上進行邏輯綜合及實現。這里采用免費的MC805lIP核,通過對MC8051結構原理的分析,詳細論述其在FPCA中的實現及應用。

2 MC8051 IP核基本結構及原理

MC8051是與MCS一5l系列微處理器指令集完全兼容的8位嵌入式微處理器,通過芯核重用技術,可廣泛應用在一些面積要求比較苛刻,而對速度要求不是很高的片上系統中。

2.1 MC8051功能特點

采用完全同步設計:指令集和標準8051微控制器完全兼容;指令執行時間為l~4個時鐘周期,執行性能優于標準805l微控制器8倍左右;用戶可選擇定時/計數器、串行接口單元的數量,最多可增加到256組;新增特殊功能寄存器用于選擇不同的定時/計數器、串行接口單元;可選擇是否使用乘法器(乘法指令MUL);可選擇是否使用除法器(除法指令DIV);可選擇是否使用十進制調整功能(十進制調整指令DA);I/0口不復用,無雙向數據I/O端口,輸入、輸出端口獨立;內部帶256Byte RAM;⑾最多可擴展至64 KB的ROM和64 KB的RAM;與工藝無關,可通過修改VHDL源代碼擴展及參數化設置。

2.2 MC8051結構及設計層次

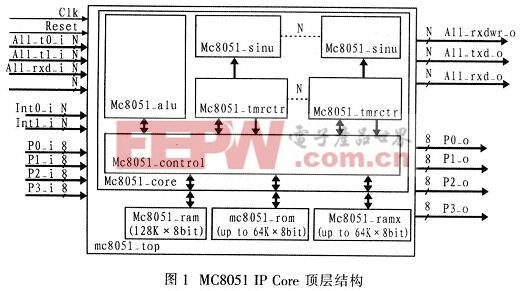

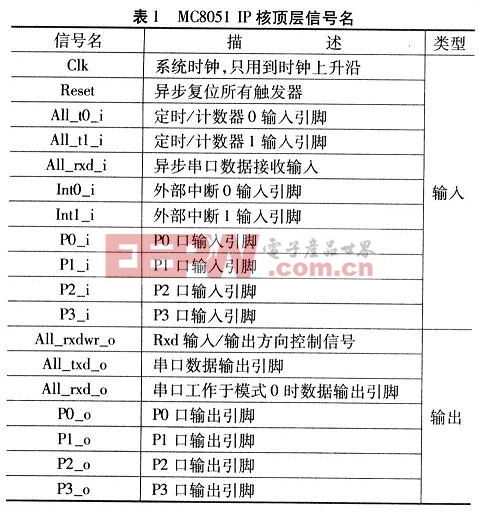

圖1給出MC805l_eore的頂層設計模塊及其子模塊,包括頂層的各個信號端口及3個存儲器模塊。同時給出了頂層的輸入輸出I/O口。定時/計數器和串行接口單元,對應于圖中的MC805l_tmrctr和MC8051_siu模塊,數量可選擇,圖中用虛線表示。MC8051 IP核與工業標準8051單片機不同,MC8051的輸入、輸出并口分別映射到獨立的端口上。其頂層各I/O信號的描述如表l所示。

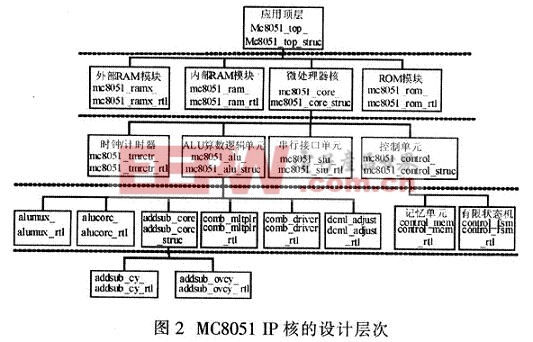

MC805lIP核的設計層次及對應的VHDL文件如圖2所示嘲。它由定時/計數器、ALU算數邏輯單元、串行接口單元和控制單元組成。RAM及ROM模塊不包括在IP核內,處于設計的頂層,方便于不同的應用設計及仿真。

圖2中,最頂層是用戶的實際應用設計模塊,它將ROM、RAM及mc8051_core封裝在內部。實際應用中用戶可添加自定義附加邏輯模塊,與設計層次中的RAM、ROM模塊處于同一個層次。

2.3 MC8051硬件模塊

單片機作為一個大型設計,其內核由定時器時鐘管理單元、ALU算數邏輯單元、串口及控制單元、存儲單元RAM及ROM等模塊組成。

2.3.1 時鐘管理單元

MC8051內核采用完全同步的時鐘設計。只有一個時鐘信號控制每個存儲單元的輸入。沒有使用門時鐘,時鐘沒有輸入到任何組合邏輯單元。中斷輸入線使用兩級同步(鎖存2次)與全局時鐘同步。可以達到完全同步,即使用其他時鐘的外部電路在驅動。并行I/0端口沒有采用這種同步方式。

2.3.2 定時器、串口和中斷

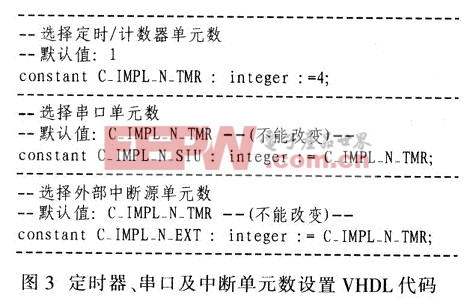

標準8051微控制器只提供兩個定時/計數器單元、一個串口單元及兩個外部中斷源。而在MC805l IP核中,這些單元最多可增加到256組,只需修改VHDL源代碼增加兼容的單元數。在VHDL源程序文件mc8051_p.vhd中,更改C_IMPL_N_TMR、C_IMPL_N_SIU、C_IMPL_N_EXT的常量值就可以,其范圍是1~256。相關的VHDL代碼如圖3所示。

這里C_IMPL_N_TMR、C_IMPL_N_SIU、C_IMPL_N_EXT3個常量參數不能獨立修改數值,只能同時增減。C_IMPL_N_TMR加l意味著對應的添加了2個定時/計數器、一個串口單元和2個外部中斷源。為了能尋址所生成的單元而不改變微控制器的地址空間,在微控制器的特殊功能寄存器(SFR)內存空間增加了2個8位寄存器作為附加功能寄存器:分別是TSEL(定時/計數器選擇寄存器,地址為Ox8E)和SSEL(串口選擇寄存器,地址為Ox9A)。如果以上的寄存器指向不存在的器件單元,將使用默認的l單元,如果沒有對這兩個寄存器賦值,其缺省值為1。如果在中斷發生期間設備(寄存器)沒被選中(比如TSEL),那么相應的中斷標志位將保持置位,直到執行中斷服務程序。

2.3.3 存儲器接口單元

由于采用優化結構設計,存儲器采用同步結構,限制輸入、輸出的時序,因而存儲器輸入、輸出數據沒用寄存器寄存。

2.3.4 可選擇指令

在某些場合,有些指令是用不到的,因此,通過禁用這些指令節省片上資源。這些指令有8位乘法器(MUL)、8位除法器(DIV)和8位十進制調整器(DA)。禁用時只需要在VHDL源程序文件MC8051_p.vh中將C_IMPL_MUL(乘法指令MUL)、C_IMPL_DIV(除法指令DIV)或C_IMPL_DA(十進制調整指令DA)的常量值設置為0即可。如果這3條可選指令沒有被執行,器件可節省約10%的資源。相應的VHDL程序代碼段如圖4所示。

[next]

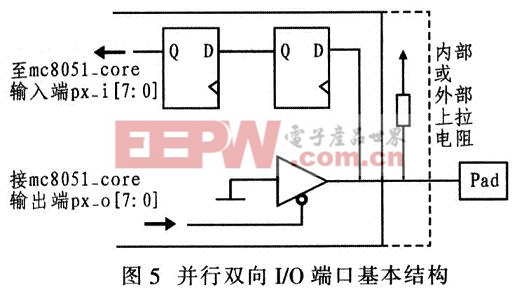

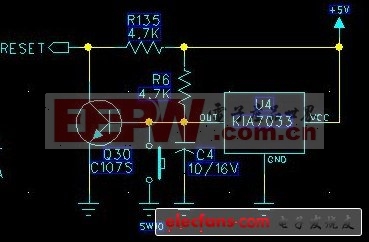

2.3.5 并行I/O端口

為了便于IC設計,MC805l IP核的I/0口不提供復用功能,包括4個8位輸入輸出口、串行接口、計數器輸入端和擴展存儲器接口。如果要想將。MC8051 IP核的并行I/O端口改為雙向I/0端口,設計時可以添加一些外圍邏輯電路來實現。其基本電路結構如圖5所示。圖中的2個D觸發器起同步輸入信號的作用(mc805l_core的輸入I/O不做同步處理),也可以不用。上拉電阻是必要的,因為I/0端口輸出高電平是靠上拉電阻實現的。

2.4 MC8051其他說明

(1)MC8051 IP核的定時器和串口波特率的計算與標準8051一樣,由系統時鐘經12倍分頻獲得計數時鐘。

(2)外部中斷信號是經兩級寄存器做同步處理后輸入的。

(3)MC805l_core的輸入I/0不做同步處理,必要時可自行添加,如圖5所示。

(4)寫應用程序時,I/O端口如果沒有做成雙向端口,而是輸入和輸出分開的,應特別注意諸如Pl=一P1、P1^O=P1^0這樣的I/0取反操作是無效的,因為讀回的值不是I/O寄存器的值,而是輸入引腳的狀態。

3 MC8051的RTL封裝

利用綜合工具Synplify Pro軟件實現對MC8051核的RTL封裝,從而生成最終所需的MC8051 IP核(.vqm文件)。

3.1 MC8051存儲模塊生成

MC8051中所需的存儲模塊:內部RAM、擴展RAM和ROM。其中內部RAM和ROM是必要的,內部RAM固定為128字節,ROM最大可選64 K字節,鑒于FPGA片上RAM資源有限,這里選用4 K字節(可根據需要修改);擴展RAM是可選,最大也可以達到64 K字節,這里選用2 K字節。

由于采用Altera公司的FPGA來實現,所以可以利用Al—tera公司的集成開發環境Quartus II來創建ROM、RAM模塊。在具體的FPGA實現中,可根據不同廠家的器件,用廠家提供的工具來生成ROM和RAM,或者采用HDL描述實現。

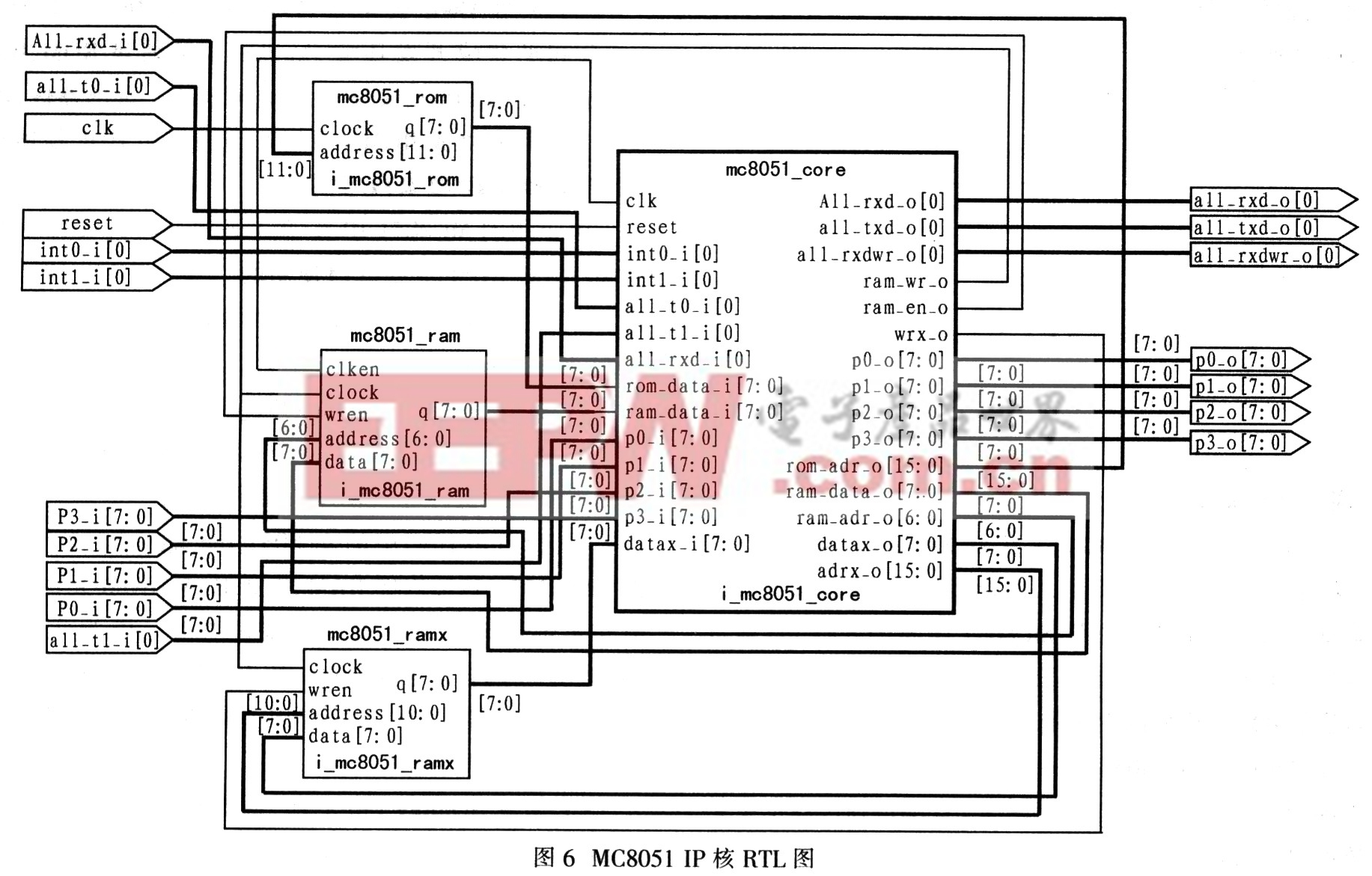

3.2 MC8051 IP核RTL封裝

由于用的MC8051 IP核源代碼頂層設計文件中的存儲模塊(RAM、ROM)是仿真時使用的,實際應用設計時,必須改成實際應用中用到的RAM、ROM模塊(也就是前面生成的RAM、ROM模塊)。

(1)打開源代碼中的mc805l_p.vhd程序包文件,將原文件中的RAM(包括內部RAM、擴展RAM)、ROM元件例化語句全部替換成實際應用設計的程序代碼;

(2)打開源代碼中的mc805l_top_stru.vhd文件,將原文件中的RAM(包括內部RAM、擴展RAM)ROM元件端口映射語句全部修改成應用設計的端口映射。因為實際應用中RAM、ROM的容量與MC8051核中存儲器容量不一致及控制信號的差異,需要修改實際應用中RAM、ROM的地址線及控制信號線的端口映射。

(3)新建Synplify Pro工程,將修改后的MC8051 IP核的VHDL文件添加到工程中。選擇綜合的目標FPGA器件,設置相關綜合參數,生成MC8051 IP核的RTL封裝文件.vqm,其綜合后的RTL圖如圖6所示。

點擊看原圖

(4)因為VHDL文件編譯是有順序的,所以在向SynplifyPro工程添加VHDL源代碼文件時,應注意的是:首先添加MC805l_p.vhd文件,然后添加其他文件,最后添加mc805l_top_.vhd和mc8051_top_strut.vhd文件。注意文件名后為_cfg.vhd的配置文件可以不添加到工程中,前面生成的RAM、ROM源代碼文件也不必添加到工程里面。

(5)綜合編譯成功后,需要檢查頂層設計是否正確,這時可通過RTL圖來檢查。在RTL圖中可看到MC8051 IP核的頂層結構圖。在RTL圖中主要檢查ROM、RAM模塊的連線是否正確,是否符合實際應用設計。

4 MC8051 IP核應用構建

采用Ahera公司的FPGA實現,可以利用Ahera公司的集成開發環境0uartus II構建實際應用系統。

4.1 MC8051硬件系統構建

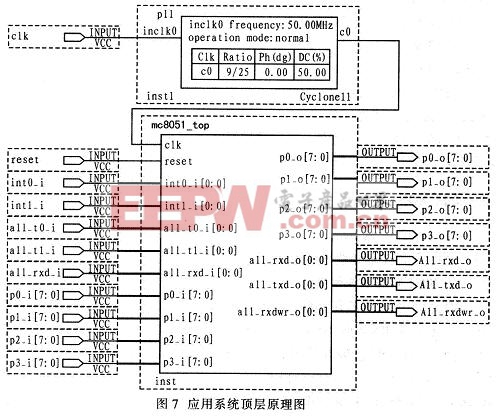

在QuartusⅡ中新建應用工程,創建頂層圖形設計文件并保存。

(1)將MC8051 IP核進行RTL封裝時用Quartus II創建的RAM、ROM模塊文件添加到工程中;

(2)在工程中調用FPGA自帶的PLL數字鎖相環模塊,將目標系統板上的時鐘調整到MC805l IP核的應用時鐘頻率。MC805l IP核經Quartus II綜合編譯后,查看時序分析報告,其最高運行頻率為18.96 MHz(每次編譯都可能不同,I/0分配不同結果可能不同),因此系統時鐘不能超過時序報告的時鐘最高頻率(即fmax)。可以選擇18 MHz,利用PLL對目標系統板上的時鐘進行分頻;

(3)將Synplifyr Pro綜合生成的RTL封裝文件.vqm拷貝到Quartus II工程文件目錄下,并添加到工程中。然后再將添加.vqm文件生成MC8051_top.bsf圖形文件;

(4)打開創建的應用設計頂層圖形設計文件,將前面生成的PLL模塊、MC8051_top模塊添加到頂層設計文件中。添加輸入/輸出引腳,并對引腳命名,連接引腳與各模塊.設置相關編譯參數。生成FPGA的配置文件*.sof。其實際應用系統頂層原理圖如圖7所示。

可將并行I/O端口設計成雙向I/O端口,以節約FPGA的引腳資源,其方法參見圖5。根據實際應用的需要,利用FPGA剩余的資源,添加其他邏輯模塊,與MC8051 core模塊、PLL模塊一起構成應用系統。這里只討論MC8051 IP核的FPGA實現。

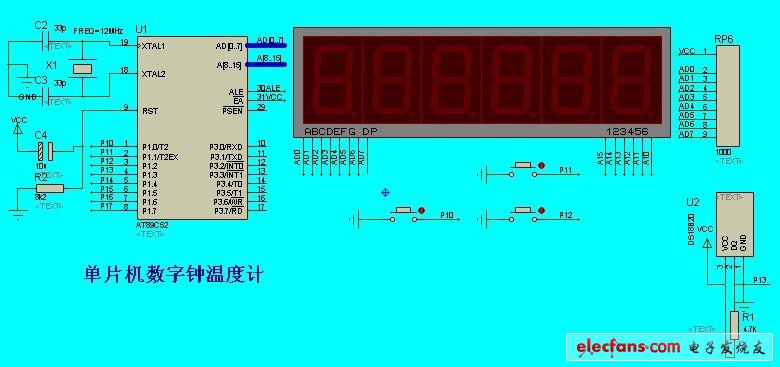

4.2 MC8051應用程序創建

在MC8051應用系統建立后,根據具體應用編寫應用程序。可以是C語言程序,也可以是匯編語言程序。MC8051的應用程序與標準的8051應用程序完全兼容,可以采用熟悉的開發工具進行應用程序的編寫。在編寫完成、仿真調試通過后,利用編譯工具編譯生成.hex文件,供固化ROM使用。

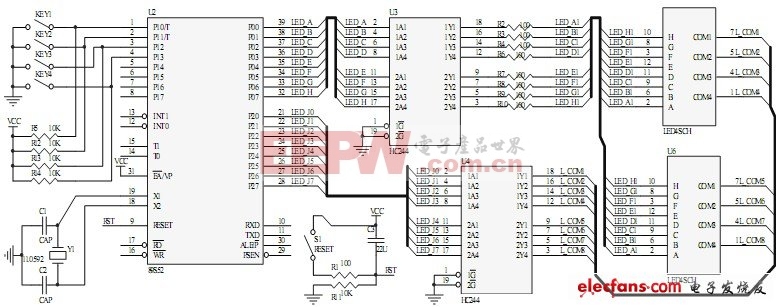

4.3 MC8051實際應用系統實現

將生成的.hex應用程序文件拷貝到Quartus II工程文件目錄下,替代原創建ROM存儲器模塊時使用的初始化.hex文件。然后重新編譯Quarius II工程生成FPGA的配置文件.sof,將應用程序代碼嵌入(同化)到ROM中。最后利用Quartus II的Programmer將FPGA的配置文件.sof下載到FPGA或EPCS中,實現MC8051的實際應用系統。

5 結語

本文在分析了MC805lIP Core的結構原理,設計層次,內核各組成模塊及參數設置的基礎上,詳細論述了MC8051 IP核的FPGA實現與應用的實際設計步驟。試驗驗證,根據需求修改后的MC8051 IP核,能很好滿足對8051MCU的應用需求,而且其性能比標準8051 MCU高,系統集成度也比采用標準8051 MCU構成的應用系統高。因此,MC8051 IP核在基于可編程邏輯和MCU的應用領域中具有廣泛的應用前景。

評論