基于51單片機和FPGA的簡易數字存儲示波器設計

5.3.3 波形存儲控制模塊

該模塊為RAM模塊的寫地址累加器,可控制波形的存儲。H_sering為單次和多次觸發控制引腳,當為高電平時,單次觸發,停止向RAM寫入數據,所顯示波形為存儲波形;為低電平時,多次觸發,當檢測到一次觸發時,即向RAM寫一次數據,共l K個點,并在寫操作時屏蔽觸發。寫地址先寫奇地址,存入通道一采樣后的波形數據,后寫偶地址,存入通道二采樣后的波形數據。如果連續多次檢測不到觸發時,向RAM中寫入全0,顯示一條直線,即實現自動捕捉功能。波形存儲控制模塊如圖5所示。

5.3.4 波形顯示控制模塊

該模塊為讀地址累加器,從RAM中讀取數據,并產生行掃描和列掃描數據。通過單片機寫入累加器基地址,改變讀取數據的起始位,實現波形的平移。該模塊還可計算波形的峰峰值、平均值,單片機可直接讀回數值。波形顯示控制模塊如圖6所示。

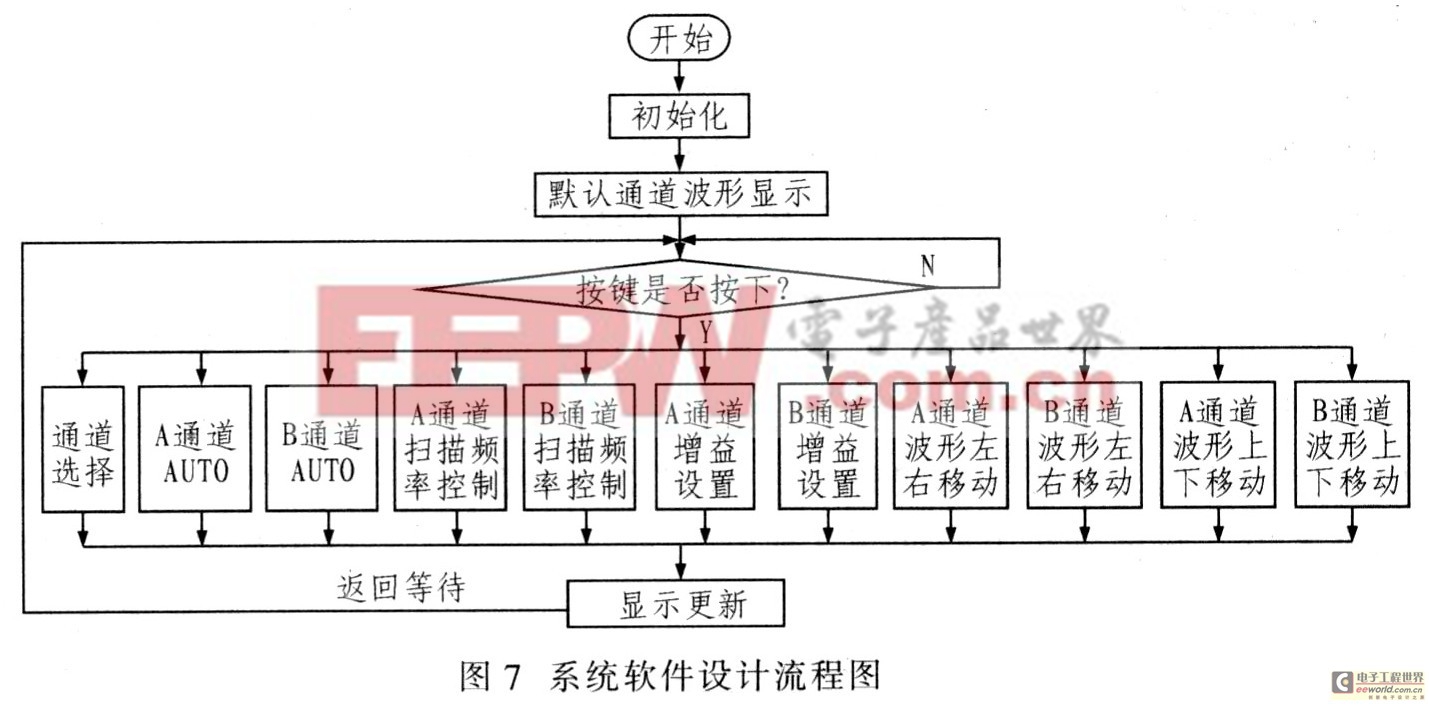

6 系統軟件設計

系統軟件設計實現人機交互、信息提示、系統啟動與復位等功能。首先系統初始化,顯示默認通道波形,再等待按鍵按下。當按鍵按下后,完成相應功能,顯示相應波形,然后循環等待。系統軟件設計流程如圖7所示。

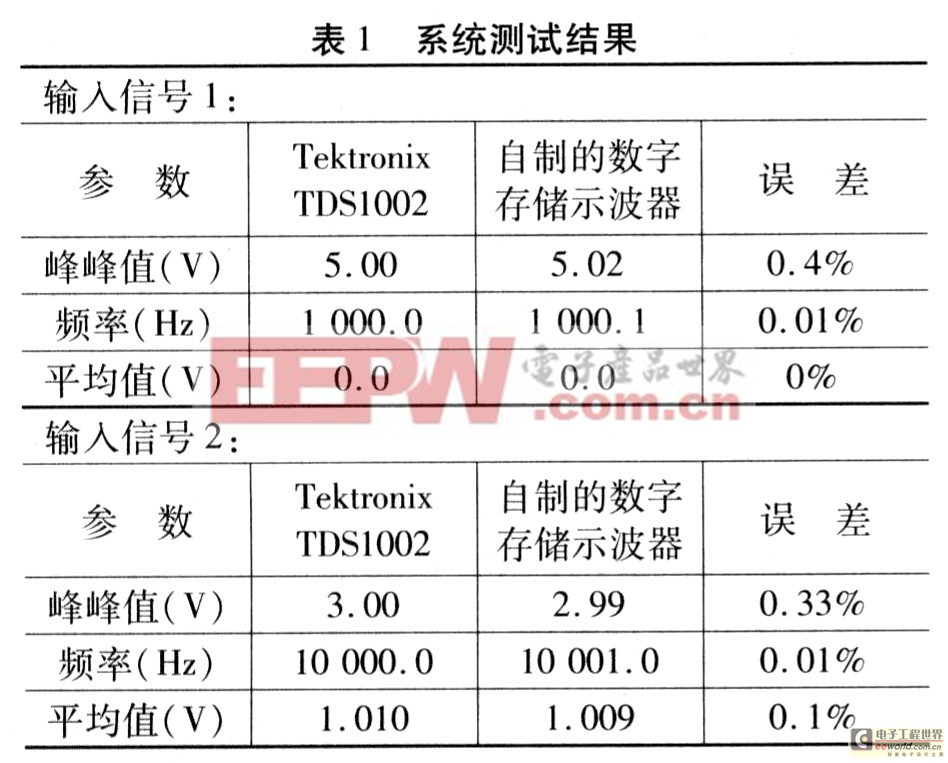

7 測試結果

使用自制的數字存儲示波器和tektronix TDSl002型數字示波器測量輸入信號,其中部分測量數據如表1所列。

通過對比測試和結果分析,各種輸入信號在自制數字存儲示波器上可精確顯示波形,并且實現波形的雙蹤顯示及波形水平、垂直平移,頻率、平均值、峰峰值的測量,誤差小,達到一定的精度要求。

8 結語

本系統設計采用單片機作為核心控制器,充分利用FPGA的可編程邏輯功能,完成相關電路設計。軟硬件有機結合實現簡易數字存儲示波器的設計,系統總體功能完善,穩定性高,使用方便。

評論