一種嵌入式的實時視頻采集系統

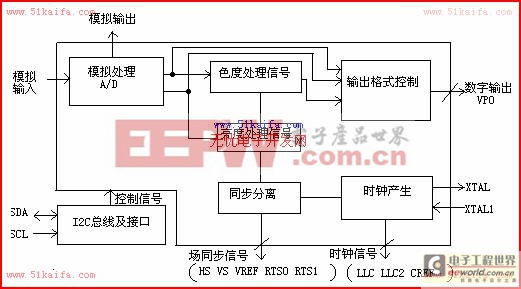

圖2 SAA7111A功能方框圖

SAA7111A的主要特點:

(1) 可編程選擇四路視頻輸入的一路或兩路,組成不同的工作模式,在其內部有兩路模擬視頻信號處理通道,可進行靜態增益控制或自動增益控制,還有兩路模數轉換器;

(2) 可對芯片編程進行自電平控制、抗混疊濾波、梳狀濾波;

(3) 場頻50Hz或60Hz自動檢測,并在PAL和NTSC制之間自動切換;

(4) 能對不同輸入制式的亮度信號和色度信號進行處理,并實現亮度、色度和飽和度的片內控制;

(5) 提供兩種數據方式供選擇,這兩種數據方式分別是RGB和YUV,可靈活輸出不同的數字圖像數據格式,主要有:4:1:1的YUV格式(12bit ), 4:2:2的YUV格式(16bit), 4:2:2的YUV格式[CCIR-656](8bit), 5:6:5的RGB格式(16bit)和8:8:8的RGB格式(24bit);

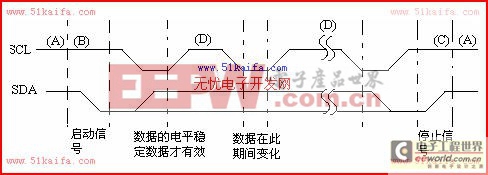

(6) SAA7111A的工作模式由其內部的控制寄存器決定,需根據不同的視頻標準來配置相應的內部寄存器,即初始化。用戶根據I2C 總線協議,將需要的控制字寫入控制地址即可對SAA7111A進行相應的控制。這些控制包括:圖像數據輸出格式、色彩、明暗、飽和度及各種參考信號的輸出。I2C總線傳送數據的基本時序如圖3所示。

圖3 I2C總線的基本時序

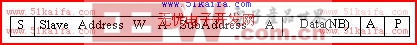

總線上的數據傳輸可以是讀或寫兩種方式,其寫格式為:

其中:S為總線起始信號;Slave Address W為被控器SAA7111的尋址字節;A為被控器應答信號;SubAddres為SAA7111控制寄存器的地址;Data(NB)即控制寄存器的配置參數;P為總線終止信號[3]。

3.3 FPGA的采集控制原理

SAA7111A的輸出時鐘信號包括LLC(27MHz)和LLC2(13.5MHz),其中LLC2為像素時鐘頻率,每一時鐘對應一個16位像素輸出。行參考同步信號HREF,高電平表示一行的有效像素,為720個LLC2周期。場參考同步信號VREF高電平時表示輸出是有效行圖像,單場是286 行;低電平期間為場消隱信號,是26個行周期。RTSO=1時表示輸出為奇數場,RTSO=0時為偶數場[4]。輸入信號FEI為輸出使能信號,為0時允許數據輸出,為1時數據輸出處于高阻狀態。圖4,5分別為采集一行和奇數場圖像的信號時序圖。

評論