基于PCI接口的高速數字信號處理板卡的設計

4 SBSRAM接口設計

SBSRAM即同步突發靜態存儲器,其最大的優點是讀寫速度高、不需要刷新。在步突發模式下,只要外部器件給出首次訪問地址,則在同步時鐘的上跳沿,就可以在內部產生訪問數據單元的突發地址,協助那些不能快速提供存取地址的控制器加快數據訪問的速度。由于TMS320C6701的EMIF(擴展存儲器接口)可以按SBSRAM的速度提供地址,所以應當將SBSRAM的突發模式禁止(/ADV接高電平)。但這一點并不意味著降低讀寫性能。事實上由于DSP在每個數據訪問周期都可以連續地輸出新的地址和控制命令,仍然能實現突發模式下的峰值讀寫速度。由于對SBSRAM存取訪問的同步時鐘頻率在80MHz,所以高速數字信號在線路板上傳輸的質量特別重要[2]。

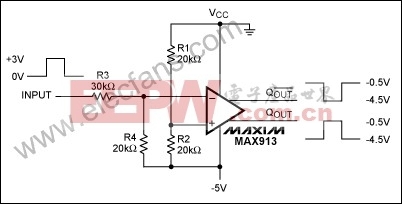

在進行PCB設計時,信號完整性(SI,Signal Integrity)必須引起重視。它主要包括反射、振鈴、地彈、串擾等。以前進行高速PCB設計時,對用戶經驗要求很高,現在借助于EDA輔助軟件,信號完整性問題可以在設計中預見,并且采用一定的措施去控制。根據所選PCB的基材(介電常數、板厚),利用Agilent公司提供的免費軟件AppCAD很容易計算傳輸線的阻抗,然后計算出最佳的端接匹配電阻。

在完成PCB設計后,利用HyperLynx的BoardSim功能可以驗證設計。BoardSim采用流行的IBIS模型(Input/Output Buffer Information Specification),在仿真時應先將器件的IBIS模型加載到指定的端口中,設置時鐘的頻率與系統的工作頻率相等,連接好示波器的探頭,啟動仿真就可以看到仿真的結果。圖3是沒采用端接電阻的仿真波形,可以看到信號質量非常差,振鈴和過沖現象嚴重。圖4是采用33Ω串行電阻端接的仿真波形,振鈴和過沖現象都有了很大的改善,信號質量較好。

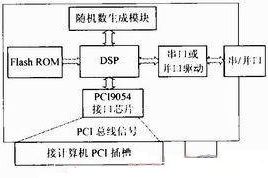

5 DSP信號處理流程

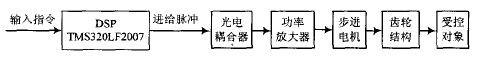

DSP信號處理算法主要依據參考文獻[1]和[3],對信號進行時間和頻率二維相關運算。時間維上的峰值可以計算出目標的距離,在頻率維上的峰值可以計算出目標的速度。信號處理流程如圖5所示。

將PCI接口應用到DSP系統中,加速了數據傳輸的速度,可以充分運用PC機平臺上豐富的軟件和硬件資源,完成數據融合、目標顯示、參數設置等任務。將運算量大的、實時性強的任務交給DSP芯片完成,充分利用了DSP芯片的特長,從而實現了PC機與DSP系統的優勢互補。二者的有機結合可以構建以個實時性強、界面友好、操控方便的信號處理系統。

評論