單片機(jī)與FPGA實(shí)現(xiàn)等精度頻率測(cè)量和IDDS技術(shù)設(shè)計(jì)方案

2.等精度頻率計(jì)的實(shí)現(xiàn)

為了減小誤差,得到高的測(cè)量精度,我們采用多周期同步測(cè)量法,即等精度測(cè)量法,通過對(duì)被測(cè)信號(hào)與閘門時(shí)間之間實(shí)現(xiàn)同步化,從而從根本上消除了在閘門時(shí)間內(nèi)對(duì)被測(cè)信號(hào)進(jìn)行計(jì)數(shù)時(shí)的 l量化誤差,使測(cè)量精度大大提高,是在測(cè)量領(lǐng)域用得比較多的的一種精度很高的測(cè)量方法。

2.1 頻率測(cè)量總體設(shè)計(jì)與方案

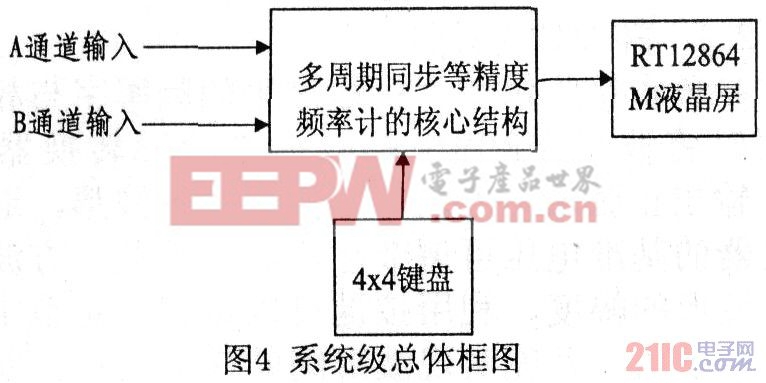

本系統(tǒng)主要是以凌陽(yáng)單片機(jī)和FPGA為核心,多周期同步等精度測(cè)量頻率計(jì)的核心結(jié)構(gòu)用VHDL硬件描述語言對(duì)FPGA進(jìn)行編程,實(shí)現(xiàn)頻率、周期、脈沖寬度和占空比的測(cè)量。而單片機(jī)則作為控制部分實(shí)現(xiàn)了頻率計(jì)的控制、掃描和顯示,系統(tǒng)級(jí)框圖如下圖4:

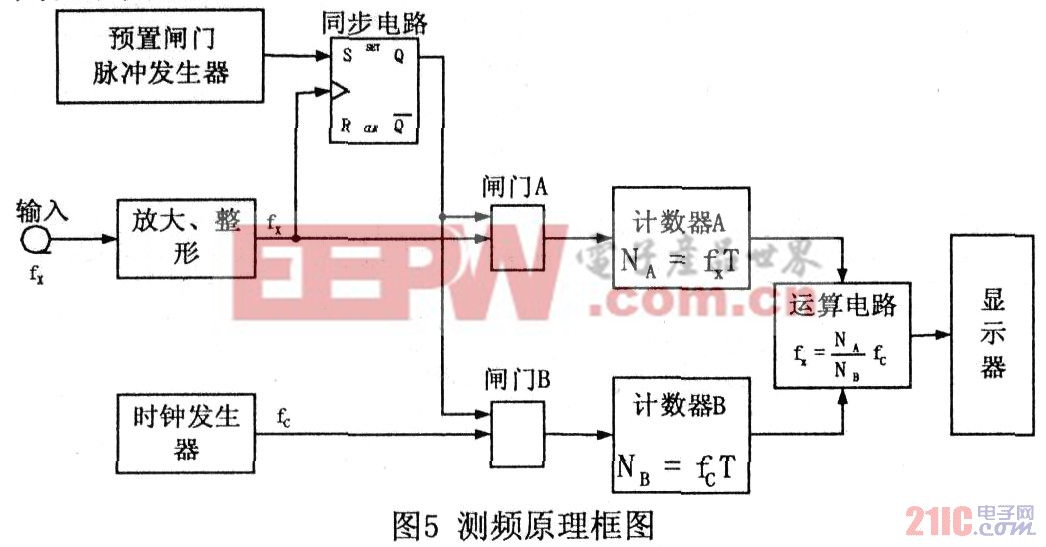

本設(shè)計(jì)頻率測(cè)量方法的主要測(cè)量原理如圖5所示,圖中預(yù)置門控信號(hào)GATE是由單片機(jī)發(fā)出,GATE的時(shí)間寬度對(duì)測(cè)頻精度影響較少,可以在較大的范圍內(nèi)選擇,只要FPGA計(jì)數(shù)器在計(jì)100M信號(hào)不溢出都行,根據(jù)理論計(jì)算GATE的時(shí)間寬度Tc可以大于42.94s,但是由于單片機(jī)的數(shù)據(jù)處理能力限制,實(shí)際的時(shí)間寬度較少,一般可在l0~0.1s間選擇,即在高頻段時(shí),閘門時(shí)間較短;低頻時(shí)閘門時(shí)間較長(zhǎng)。這樣閘門時(shí)問寬度Tc依據(jù)被測(cè)頻率的大小自動(dòng)調(diào)整測(cè)頻,從而實(shí)現(xiàn)量程的自動(dòng)轉(zhuǎn)換,擴(kuò)大了測(cè)

頻的量程范圍;實(shí)現(xiàn)了全范圍等精度測(cè)量,減小了低頻測(cè)量的誤差。

2.2 測(cè)頻輸入級(jí)的設(shè)計(jì)

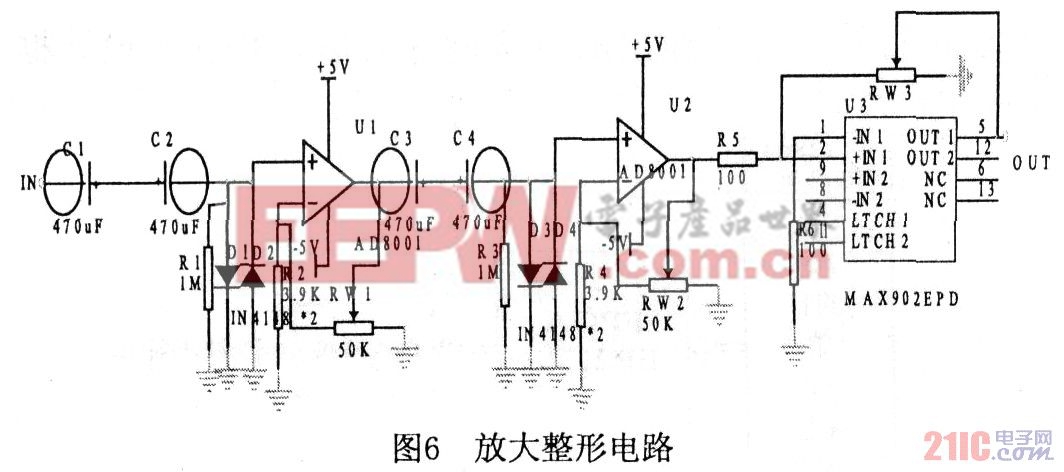

由于輸入的信號(hào)幅度不確定、波形不確定、邊沿不夠陡峭,而FPGA只處理TTL電平的信號(hào),因此我們必須對(duì)輸入信號(hào)進(jìn)行放大、整形處理。詳細(xì)設(shè)計(jì)的電路圖如圖6所示。

評(píng)論