單片機與CPCI總線的脈沖信號檢測系統設計

2.3 接口處理FPGA

由于需要對80路脈沖信號進行檢測,采用單片機無法滿足并行處理的需求,因此選用FPGA完成脈沖采樣功能。接口處理FPGA采用Altera公司的FLEX10K50,工作主頻為6 MHz,存儲芯片采用EPC1PC8。

其主要功能有三部分:分頻定時器、采樣數據緩存、外圍控制邏輯。FPGA對主時鐘進行分頻,形成周期為1 ms的時鐘信號。FPGA每ms對80路脈沖信號完成并行采集一次,將數據存放在寄存器中,同時向單片機發出中斷信號,通知單片機發起數據搬移,以及單片機內部的時間計數器自增。采樣數據緩存模塊用于將80路脈沖信號同時鎖存至內部寄存器,單片機每ms全部讀取一次。外圍控制邏輯用于單片機外圍各控制信號的譯碼,包括控制寄存器、各芯片控制信號譯碼,以及其他輔助功能的實現。

2.4 單片機系統

單片機系統采用Atmel公司的AT89C51,配合32KB外部SRAM 62256以及4 KB雙口數據RAMIDT71342。其中,CPCI總線訪問雙口數據RAM的L端口,8051訪問R端口。

單片機工作主頻設計為20 MHz。單片機P0口和P2口作為通用的數據線和地址線使用,配合地址鎖存器74HC373 工作;P1口不使用;P3口中僅使用了P3.2用于接收外部中斷,即來自接口處理FPGA的中斷。FPGA內部定時器每ms產生一個中斷脈沖,用于單片機軟件計時器的激勵時鐘,同時通知單片機讀取脈沖信號接口采樣數據。

單片機的外部地址空間劃分如表1所列。

單片機產生的脈沖信號數據幀格式如圖4所示。每個數據幀包含14個字節數據,時間碼為4個字節,加電后從0開始計時,單位為ms;采樣脈沖數據共10個字節,對應80路脈沖信號。

2.5 PCI總線接口

板卡采用CPCI接口方式,接口芯片采用PLX公司的PLX9052,與配置EEPROM芯片93CS46配合使用。板卡在PCI總線中工作在從模式下。接口芯片對部數據總線選擇低8位數據線與雙口 RAM連接,測試客戶機定期查詢每塊測試板卡中雙口RAM的工作模式,不使用本地中斷信號。

3 軟件設計

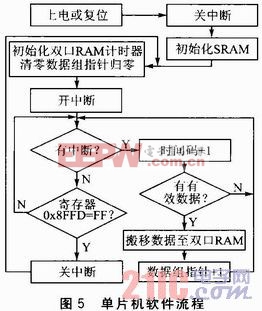

脈沖信號檢測板單片機軟件主要完成脈沖采樣數據的處理,剔除FPGA產生的采樣數據中的無效數據,將檢測到的脈沖有效數據打上時間標簽后存儲到雙口數據RAM中。雙口 RAM中循環存儲256組脈沖信號數據,測試客戶機定期訪問雙口RAM,讀取檢測數據。單片機軟件流程如圖5所示。

圖5中寄存器0x8FFD為配置寄存器,由測試客戶機軟件寫入,用于初始化雙口RAM中的數據。

結語

本文提出的兩級測試系統的沒計思路和基于單片機與CPCI總線的脈沖信號檢測系統沒計方案,可以適應較寬電壓幅度范圍的接口電平信號。系統采用標準的CPCI總線接口,具有良好的兼容性和擴展性,能較好地滿足對脈沖信號的功能測試。如需要提高測量精度,可縮短FPGA采樣間隔來實現。

目前,該方案已經大量應用于產品測試和系統集成測試中。

評論