EmbeddedICE目標(biāo)系統(tǒng)中的調(diào)試功能擴(kuò)展部件

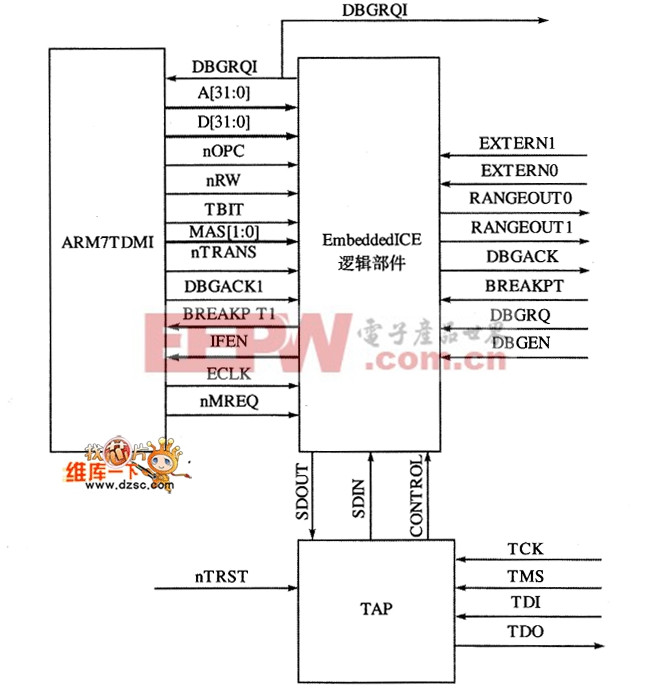

圖 處理器內(nèi)核、EmbeddedICE邏輯部件及TAP控制器之間的關(guān)系

EmbeddedICE邏輯部件包括:

·兩個(gè)數(shù)據(jù)斷點(diǎn)(watchpoint)寄存器。

·兩個(gè)獨(dú)立的寄存器,即調(diào)試寄存器和調(diào)試狀態(tài)寄存器。

·調(diào)試通信通道(DCC)。

兩個(gè)數(shù)據(jù)斷點(diǎn)寄存器可以被用來(lái)設(shè)置斷點(diǎn)或程序斷點(diǎn)。當(dāng)設(shè)置程序斷點(diǎn),地址與數(shù)據(jù)斷點(diǎn)寄存器的值相等時(shí),EmbeddedICE邏輯部件停止程序的執(zhí)行;當(dāng)前指定的當(dāng)設(shè)置數(shù)據(jù)斷點(diǎn),當(dāng)前數(shù)據(jù)總線上的數(shù)據(jù)與數(shù)據(jù)斷點(diǎn)寄存器的值相等時(shí),EmbeddedICE邏輯部件停止程序的執(zhí)行。

與基于Angel的調(diào)試系統(tǒng)不同,這時(shí)程序斷點(diǎn)可以設(shè)置在ROM中,這是因?yàn)镋mbeddedICE邏輯部件提供了所需要的硬件支持。

在數(shù)據(jù)斷點(diǎn)寄存器中的數(shù)據(jù)位可以被屏蔽,使其在進(jìn)行比較時(shí)不起作用,從而使得斷點(diǎn)的設(shè)置更為靈活。

調(diào)試通信通道(DCC)用來(lái)在主機(jī)上的調(diào)試器與目標(biāo)處理器之間建立通信通道。在ARMTTDMI中,它是作為一個(gè)協(xié)處理器實(shí)現(xiàn)的。它包括:

·一個(gè)32位的通信數(shù)據(jù)讀取寄存器。

·一個(gè)32位的通信數(shù)據(jù)寫(xiě)入寄存器。

·一個(gè)6位的通信控制寄存器。

通過(guò)這些接口,DOC可以在主機(jī)上的調(diào)試器和目標(biāo)處理器之間建立通信信道。

在所有調(diào)試信號(hào)中,下面3個(gè)是最主要的。

●BREAKPT:終止處理器進(jìn)入調(diào)試狀態(tài)。

●DBGRQ:請(qǐng)求處理器進(jìn)入調(diào)試狀態(tài)。

●DBGACK:表明處理器己經(jīng)進(jìn)入調(diào)試狀態(tài)。

評(píng)論