基于ARM和eCos的嵌入式WEB服務器設計

隨著現(xiàn)代通信技術和網(wǎng)絡技術的迅猛發(fā)展,以太網(wǎng)技術也越來越成熟,特別是基于TCP/IP通信協(xié)議的Web技術得到了廣泛應用。我們可以用微控制器加以太網(wǎng)接口芯片,取代PC機進行現(xiàn)場控制,組成嵌入式Web Serv-er系統(tǒng)。現(xiàn)場傳感器自動跟蹤各監(jiān)測點的信息,把檢測到的數(shù)據(jù)存儲在非易失性存儲器中,并及時發(fā)布到互聯(lián)網(wǎng)上;相關的工作人員就可以通過Web技術對設備進行遠程控制、管理和維護,從瀏覽器上直接監(jiān)控現(xiàn)場設備的運行,這樣就大大提高了生產(chǎn)效率和管理水平。

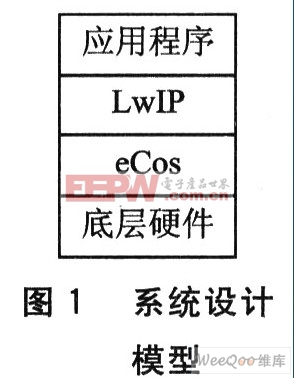

為了實現(xiàn)WEB服務器的功能,嵌入式操作系統(tǒng)和一個可實現(xiàn)的TCP/IP協(xié)議棧是必需的,因此對嵌入式處理器提出了更高的要求。與傳統(tǒng)的8/16位單片機相比,ARM核處理器在運算速度、功耗和存儲容量方面都有很大的優(yōu)勢,而且ARM核處理器可以很方便地實現(xiàn)嵌入式TCP/IP協(xié)議棧,所以ARM核處理器成為嵌入式Web服務器設備的首選處理器。系統(tǒng)的設計模型如圖1所示。

1 系統(tǒng)硬件設計

ARM核處理器LPC2210基于支持實時仿真和嵌入跟蹤的32/16位ARM7TDMI—S CPU。片內(nèi)有16 KBSRAM,通過外部存儲器接口配置成4組,每組的容量達16 MB。LPC2210采用144腳封裝,功耗極低,具有多個32位定時器、8路10位ADC、PWM輸出,最多可提供76個GPIO以及多達9個外部中斷引腳;采用3級流水線技術,極大地提高了指令執(zhí)行效率,通過可編程的片內(nèi)鎖相環(huán)(PLL)可實現(xiàn)最大60 MHz的CPU操作頻率。

LPC2210的EMC組合符合ARM公司的PL090標準,總線寬度可設置為8位、16位或32位,通常16位總線寬度的存儲器具有較高的性價比。

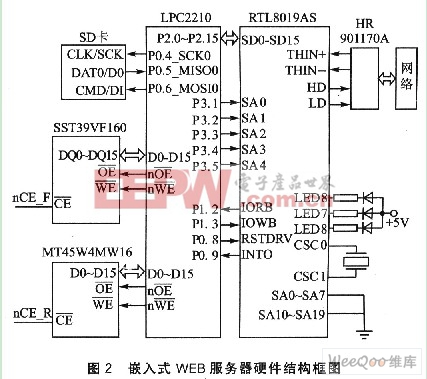

以Philips公司的ARM核處理器LPC2210為核心來實現(xiàn)嵌入式Web服務器;網(wǎng)絡接口芯片采用Realtek公司的NE2000兼容芯片RTL8019AS,它內(nèi)置了10BASE—T收發(fā)器,通過HR901170A器件接入以太網(wǎng)。硬件結(jié)構如圖2所示。

在圖1中,LPC2210擴展了2 MB的NOR Flash(芯片型號為SST39VFl60)和8.MB PSRAM(芯片型號為MT45W4Mwl6)。為了方便調(diào)試及最終代碼的固化應用,使用LPC2210外部存儲器接口BankO和Bankl的地址空間,通過片選信號選通nCE_F和nCE_R,來將地址空間Bank0和Bankl分別分配給PSRAM和Flash。通常將代碼固化到Flash,分配Flash為Bank0,PSRAM為Bankl,因為Bank0可以用來引導程序的運行。

tcp/ip相關文章:tcp/ip是什么

評論