基于大容量FPGA的多節點系統的遠程升級的實現

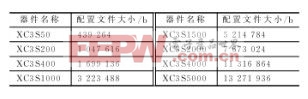

表2 Spartan3系列FPGA配置文件大小

以XC3S4000型FPGA為例,它的配置文件所需的存儲空間約為1.35 MB,已遠遠超出了ATmega64單片機的尋址空間。因此,為了能夠利用ATmega64單片機來實現對FPGA配置數據的讀寫,必須對其尋址空間進行擴展。擴展的硬件連接框圖如圖2中的單片機與Flash的連接部分所示。

本設計中是使用通用I/O來擴展ATmega64單片機的尋址空間的。ATmega64單片機的總尋址空間為64 KB,但片內4 KB的SRAM及各種寄存器占用了前面的部分尋址空間,故其片外存儲器尋址空間是0x1100~0xFFFF。因此將Flash的低15位地址直接接到ATmega64單片機的低15位地址總線上,其余6位高位地址用單片機的通用I/O進行選擇。尋址時單片機的專用地址口只輸出0x8000~0xFFFF的地址數據,與通用I/O輸出的地址組合后給出Flash的讀寫地址。

通過以上對ATmega64單片機尋址空間的擴展方法,可以實現ATmega64單片機對合適的Flash存儲器的尋址操作,從而解決了大容量FPGA配置數據的存儲和讀取問題。

2.2.3 用ATmega64實現FPGA的SELECTMAP加載

Xilinx公司的Spartan3系列FPGA加載方式分為5種: Master Serial、Slave Serial、Master Parallel、Slave Parallel、JTAG。

按照FPGA是否控制加載過程,加載方式可分為Master方式和Slave方式;按照加載數據時的數據位寬,可分為Serial方式和Parallel方式。用于加載的引腳主要有: PROG_B,CCLK,RDWR_B,DONE,INIT_B,CS_B,BUSY,D[0~7],M[0~2],HSWAP和JTAG接口(TDI、TMS、TCK、TDO)。加載過程大體分為3個步驟:配置的建立、配置數據的加載和加載完成。

SELECTMAP即Slave Parallel方式,是由外部控制器控制FPGA的加載過程,并以8位數據的形式向FPGA寫入加載數據的加載方法。圖2中FPGA與ATmega64的連接部分為ATmega64單片機采用SELECTMAP方式對FPGA進行加載的硬件連接框圖,具體實現過程如下:

ATmega64通過將FPGA的PROG_B、CS_B和RDWR_B引腳置低來開啟加載過程,FPGA在PROG_B置低后開始清除內部配置RAM,并將INIT_B腳置低。PROG_B重新置1后,在INIT_B由低變高的上升沿,FPGA采樣M[0~2]引腳獲取配置方式信息。ATmega64監視FPGA的INIT_B腳,當INIT_B腳由低變高時,說明FPGA已經完成了內部配置RAM的清除工作,并準備好接收配置數據。在ATmega64給出的CCLK配置時鐘的上升沿,配置數據D[0~7]寫入配置RAM。當FPGA接收完所有的配置數據后,DONE引腳被FPGA置為高電平。ATmega64可以通過監視DONE引腳來判斷FPGA是否加載完成。對于Spartan3系列的FPGA,如果配置FPGA的CCLK的頻率高于50 MHz,則外部控制器還需要監視FPGA的BUSY引腳。當BUSY腳為高時,說明FPGA還未完成上一個配置數據的處理,此時外部控制器需要繼續保持上一個配置數據在D[0~7]引腳,直至BUSY引腳回到低電平。對于本設計的應用,ATmega64給出的配置時鐘頻率遠低于50 MHz,不必考慮BUSY引腳的控制作用。

3 軟件設計

3.1 主控計算機的軟件設計

主控制計算機的軟件運行狀態應該分為兩種:一是平時的查詢控制狀態,用來查詢和控制系統中各個節點的工作狀態;二是系統的升級狀態,用來執行對各個子節點的升級控制。如圖4所示,這兩種狀態是可以相互轉換的。

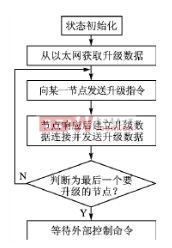

圖4 主控計算機主要狀態

軟件的查詢控制狀態,是由系統所要實現的主要功能決定的,不屬于本文所討論的范疇。在系統的升級狀態,主控計算機先要通過以太網獲得系統各個節點的遠程升級數據,待全部升級數據接收完成后,向系統的一個節點發送升級指令。節點響應并建立起通信連接后,將該節點的升級數據全部發送到該節點。接下來,主控計算機判斷上一個節點是否為最后一個需要升級的節點,如果不是,則繼續進行下一個節點升級數據的傳輸。系統所有的節點升級完成后,等待外部輸入的控制命令。例如,讓整個系統重新啟動,加載新的數據;或暫時不重新啟動而返回查詢控制狀態。軟件流程如圖5所示。

圖5 系統升級狀態流程

3.2 子節點的軟件設計

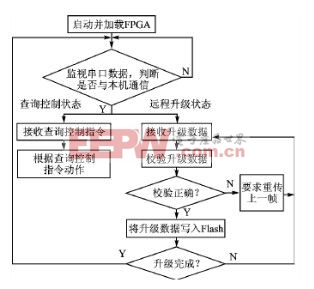

對于子節點的軟件設計,與主控計算機一樣,也分為平時的查詢控制狀態和系統升級狀態,并且它們之間也能夠與主控計算機一起相互轉換;但ATmega64單片機還要承擔對FPGA的加載任務。開機運行后,ATmega64單片機先加載子節點FPGA,使子節點能夠正常工作。子節點正常工作后,監視RS485總線并判斷有無對本節點的通信。當主控計算機要求與本節點建立通信連接時,發送反饋信息,與其建立通信連接。子節點根據主控計算機發送的命令,進入查詢控制模式或者遠程升級模式。進入遠程升級模式后,子節點接收主控計算機發來的遠程升級數據,升級數據經過校驗后寫入Flash。升級完成后繼續等待主控計算機的命令,重新啟動或繼續運行。其具體的軟件設計流程如圖6所示。

圖6 子節點軟件流程

結語

FPGA既繼承了ASIC的大規模、高集成度、高可靠性的優點,又克服了普通ASIC周期長、投資大、靈活性差的缺點,逐步成為許多系統實現的理想選擇。特別是隨著FPGA容量和性能的提升,加上其獨特的硬件升級能力,其應用范圍越來越廣。本文所提出的對大容量FPGA構成的多節點系統的遠程升級方法,系統構成簡單、技術成熟,而且具有明顯的成本優勢

評論