基于FPGA的ARM并行總線設(shè)計(jì)與仿真分析

在數(shù)字系統(tǒng)的設(shè)計(jì)中,F(xiàn)PGA+ARM的系統(tǒng)架構(gòu)得到了越來越廣泛的應(yīng)用,F(xiàn)PGA主要實(shí)現(xiàn)高速數(shù)據(jù)的處理;ARM主要實(shí)現(xiàn)系統(tǒng)的流程控制。人機(jī)交互。外部通信以及FPGA控制等功能。I2C、SPI等串行總線接口只能實(shí)現(xiàn)FPGA和ARM之間的低速通信; 當(dāng)傳輸?shù)臄?shù)據(jù)量較大。要求高速傳輸時(shí),就需要用并行總線來進(jìn)行兩者之間的高速數(shù)據(jù)傳輸。

下面基于ARM處理器LPC2478 以及FPGA器件EP2C20Q240,以ARM外部總線的讀操作時(shí)序?yàn)槔芯績(jī)烧咧g高速傳輸?shù)?a class="contentlabel" href="http://www.104case.com/news/listbylabel/label/并行總線">并行總線;其中,數(shù)據(jù)總線為32位;并在FPGA內(nèi)部構(gòu)造了1024x32bits的SRAM高速存儲(chǔ)緩沖器,以便于ARM處理器快速讀寫FPGA內(nèi)部數(shù)據(jù)。

1 ARM并行總線的工作原理

ARM處理器LPC2478的外部并行總線由24根地址總線。32根數(shù)據(jù)總線和若干讀寫、片選等控制信號(hào)線組成。根據(jù)系統(tǒng)需求,數(shù)據(jù)總線寬度還可以配置為8位,16位和32位等幾種工作模式。

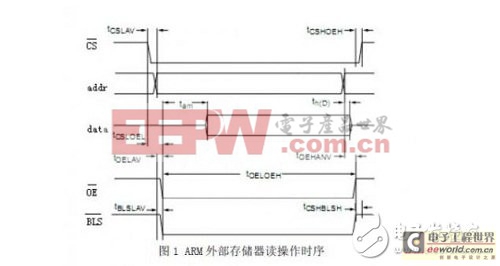

在本設(shè)計(jì)中,用到ARM外部總線的信號(hào)有:CS.WE.OE.DATA[310].ADDR[230].BLS等。CS為片選信號(hào),WE為寫使能信號(hào),OE 為讀使能信號(hào),DATA為數(shù)據(jù)總線,ADDR地址總線,BLS為字節(jié)組選擇信號(hào)。ARM的外部總線讀操作時(shí)序圖,分別如圖1所示。

根據(jù)ARM外部并行總線操作的時(shí)序,ARM外部總線的讀寫操作均在CS為低電平有效的情況下進(jìn)行。由于讀操作和寫操作不可能同時(shí)進(jìn)行,因此WE和OE信號(hào)不能同時(shí)出現(xiàn)低電平的情況。

數(shù)據(jù)總線DATA是雙向的總線,要求FPGA也要實(shí)現(xiàn)雙向數(shù)據(jù)的傳輸。在時(shí)序圖中給出了時(shí)序之間的制約關(guān)系,設(shè)計(jì)FPGA時(shí)應(yīng)該滿足ARM信號(hào)的建立時(shí)間和保持時(shí)間的要求,否則可能出現(xiàn)讀寫不穩(wěn)定的情況。

2 FPGA的并行總線設(shè)計(jì)

2.1 FPGA的端口設(shè)計(jì)

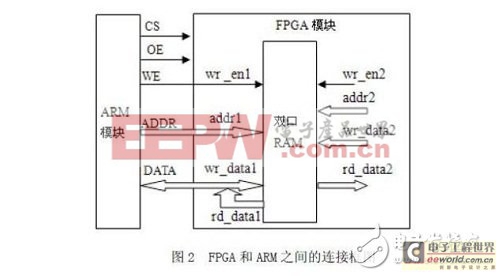

FPGA 和ARM之間的外部并行總線連接框圖,如圖2所示。由于FPGA內(nèi)部的SRAM存儲(chǔ)單元為32位,不需要進(jìn)行字節(jié)組的選擇,因此BLS信號(hào)可以不連接。為了便于實(shí)現(xiàn)ARM和FPGA之間數(shù)據(jù)的快速傳輸,F(xiàn)PGA內(nèi)部的SRAM既要與ARM處理器進(jìn)行讀寫處理,還要跟FPGA內(nèi)部的其他邏輯模塊進(jìn)行數(shù)據(jù)交換,因此SRAM采用雙口RAM來實(shí)現(xiàn)。

從端口的方向特性看,DATA端口是INOUT(雙向)方式,其余端口均為IN(輸入)方式。從端口的功能看,clk20m是全局時(shí)鐘,在實(shí)現(xiàn)時(shí)應(yīng)采用 FPGA的全局時(shí)鐘網(wǎng)絡(luò),這樣可以有效減少時(shí)鐘延時(shí),保證FPGA時(shí)序的正確性。ADDR是16位的地址總線,由ARM器件輸入到FPGA。DATA是 32位的雙向數(shù)據(jù)總線,雙向總線的設(shè)計(jì)是整個(gè)設(shè)計(jì)的重點(diǎn)。OE為ARM輸入到FPGA的讀使能信號(hào)。

評(píng)論