基于TMS320VC33-150的聲探測系統設計

引言

本文引用地址:http://www.104case.com/article/21563.htm被動聲源探測定位技術是一種利用聲學傳聲器陣列和電子裝置接收運動目標的輻射噪聲,以確定目標所處位置的技術。

本文正是基于聲探測技術原理和成熟的微電子技術, 采用ti公司的32位浮點dsp芯片tms320vc33-150來實現聲源目標的探測定位算法,并輔之以adc、cpld、單片機等器件來實現聲源信號的采集、系統邏輯控制以及通信功能。對于數字電路的邏輯控制功能,本文選用了altera公司的cpld芯片epm7128aetc100-10來實現。該芯片功耗低、資源豐富、內部延時固定,有助于時序邏輯電路的設計。本系統主要分為兩部分:聲探測系統數字電路的硬件實現和dsp軟件設計。系統現已完成調試,運行穩定,探測效果較好。

系統功能

聲探測系統通過傳聲器陣列獲得聲源目標的輻射噪聲信息,通過前端模擬信號處理后,在數字電路中由dsp進行高速的聲探測定位算法處理,并把獲得的聲源方位、速度等信息,發送給計算機終端進行交匯顯示。

聲探測系統的硬件設計

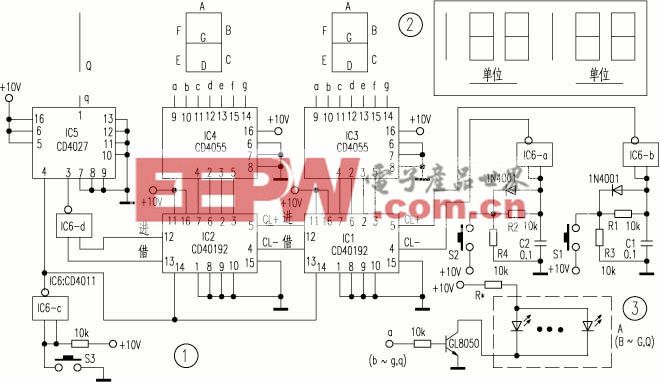

在聲探測系統中,數字電路是最為關鍵的部分。本文以dsp、cpld和單片機為核心器件,完成了聲探測系統的數字電路的硬件設計。其數字電路框圖如圖1所示。

圖1 聲探測系統的數字電路框圖 經過前端處理的模擬信號由ad7865完成采樣轉換后,給dsp一個中斷,dsp在cpld的配合下,讀取各個通道的數據并存儲在片外sram數據區,同時dsp對數據進行數字濾波、頻譜分析,從而完成對聲源目標的定位功能。

由雙口ram實現dsp和c8051f020目標信息的交換,最終通過max3485完成和終端的rs-422通信。另外,dsp根據處理后的結果實現對前端模擬電路的增益控制。

adc設計

被動聲探測系統中對聲音的相位一致性要求很高,因此,在設計中采用了具有同時采樣保持功能的14位并行輸出adc ad7865。本設計中,經放大濾波處理后的6路聲源目標信號通過兩片ad7865實現a/d轉換。本文利用dsp定時器的輸出信號作為adc的啟動采樣信號,采樣轉換完成后,通過adc的busy信號給dsp一個中斷,然后dsp進入中斷處理程序,讀取a/d數據,而讀寫信號和adc片選信號由cpld對dsp的讀寫信號和地址信號進行邏輯組合來完成。

dsp及周邊電路設計

dsp的主要功能有根據采集到的數字信號的幅度來完成對前端模擬信號的自動增益控制,增益控制的級別有16、64、256、1024、4096、16384、65536共7檔;對采集到的數據進行數字濾波、快速fft變換以及正交變換等運算,進而完成對目標的定位、識別等運算;通過雙口ram完成和單片機的通信,以及adc的定時啟動。

dsp周邊電路包括程序引導區flash、程序運行區sram、數據交換區雙口ram及增益控制。flash采用容量為1m*8b的amd29lv040b構成代碼存儲空間;sram則采用容量為512k*8b的sram存儲器cy7c1049-cv33,在電路中使用4片進行位擴展,從而構成512k*32位的程序運行空間;雙口ram為2k*8位的idt71v321;而增益控制則采用8位 cmos鎖存器來實現。

tms320vc33-150有四個外部中斷,都可以作為bootloader的中斷,因此bootloader首選高優先級的中斷,否則有可能在脫機上電加載程序時無法加載成功。因為在上電復位后,dsp執行駐留程序,根據中斷級別去尋找bootloader存儲區域,如果沒有把高于bootloader中斷的中斷置無效,那么dsp將會根據高優先級尋找bootloader存儲區域,因而導致程序加載不成功。

此外,在設計過程中,對于一些重要的信號如#rdy、#hold、edgemode、mcbl/#mp、#shz等,要根據具體設計,參照數據手冊相應給予上拉或下拉處理。本設計在調試過程中因為對#hold信號未做處理,導致不能在線下載

程序,最后通過拉高才解決。

表1 中斷號和程序裝載地址對應表

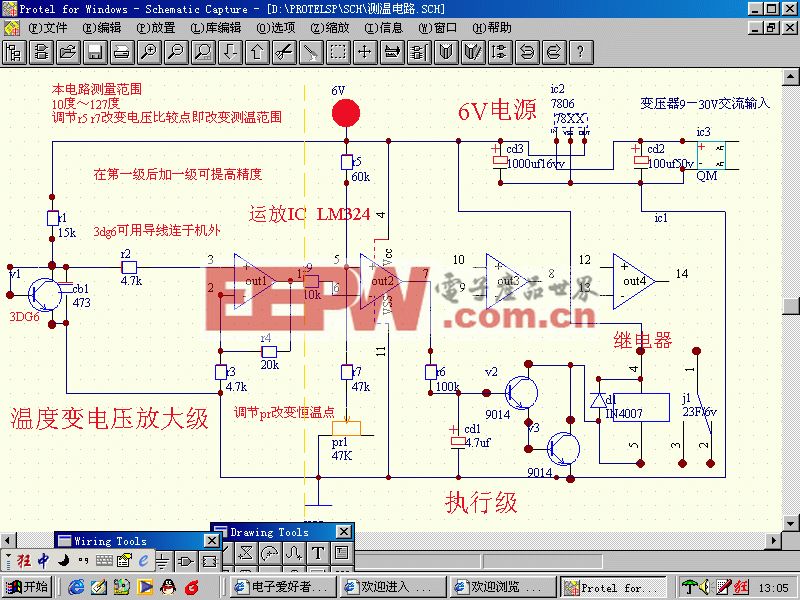

圖2 dsp軟件程序設計流程圖

邏輯控制

本設計中采用了altera公司的epm7128aetc100-10來實現整個電路系統的時序管理及邏輯控制功能,主要包括adc控制功能模塊、存儲器讀寫時序控制模塊、通信接口時序控制模塊和增益控制。并根據dsp外部存儲器地址空間譯碼產生片選信號以及讀寫時序。本設計中利用quartusⅱ來完成邏輯控制仿真。

單片機電路

c8051f020單片機是完全集成的混合信號系統級mcu,除了具有標準8051單片機的數字外設部件外,片內還集成了數據采集與控制系統中常用的模擬部件和其它數字外設及功能部件。

本設計中利用c8051f020的串口實現了和計算機終端的rs-422異步串行通信,波特率為19.2kbps;利用雙口ram完成了dsp和單片機的聲源目標數據的實時交換。

在設計單片機電路時,為保證上電復位電路的可靠性,可以使用基本的rc電路和專門的監控集成電路如max708t等,同時應該充分利用moden vdd監視器功能。

輔助電路

輔助電路包括晶振、看門狗、電壓基準電路以及dc/dc電源模塊。dsp時鐘采用了15mhz晶振,經dsp內部5倍頻后達到tms320vc33-150的最快運行速度,同時采用20mhz晶振作為單片機的時鐘源;本設計中通過采用max706看門狗芯片實現了對dsp的掉電監控和程序跑飛的復位功能;電壓基準電路則利用了tps767d318來為整個系統提供+3.3v和+1.8v電源;dc/dc電源模塊完成外接+12v~+5v的高效轉換。

dsp軟件設計

dsp軟件流程

整個軟件基于中斷方式。dsp軟件設計包括了adc的轉換啟動、數據采集、中斷服務程序、聲源信號的數字濾波、快速fft和正交變換,以及通過頻譜分析獲得高分辨率空間聲強分布的music算法。該聲探測系統的dsp軟件流程如圖2所示。

dsp軟件工作流程為:系統上電復位后,加載外部flash的程序文件到外部sram程序區,dsp初始化各個部分后運行。程序始終查詢adc的中斷信號,在獲得adc的中斷后進入中斷服務程序,采集后的數據存儲在外部sram數據區,然后調用探測定位程序獲取聲音目標的方位等參數,并寫入外部雙口ram中,供單片機讀取后送到計算機終端進行融合交會。

dsp程序bootloader

tms320vc33-150有兩種工作方式,工作方式的選擇由mcbl/mp引腳決定。在本設計中,通過把mcbl/mp引腳上拉為高電平,使dsp工作在微計算機/引導裝入模式或外部存儲器裝載方式。在reset 信號從低電平轉為高電平后, tms320vc32-150首先檢查外部中斷輸入線電平, 決定由什么地方開始引導程序, 中斷號和對應的開始引導地址間的關系如表1所示。本設計中使用了boot2方式,即在dsp復位信號由低變高后,dsp從外部存儲地址400000h開始加載程序。

需要注意的是,使用外部存儲器裝載方式時,加載程序必須含有外部存儲器的數據總線寬度(8位、16位或32位)、程序代碼的長度、程序執行的入口地址以及存儲器的等待狀態數。

在把已調試成功的程序裝入flash過程中,本文采用的方法是:通過編寫一個*.cmd轉換文件,然后用hex30.exe把*.out文件轉化為*.hex文件。 并把生成的*.hex文件燒寫入flash中即可。當然,也可采用在線燒寫的方法。

結語

基于tms320vc33-150的聲探測系統數字電路設計充分利用了tms320vc33-150強大的浮點運算能力,很好的完成了聲源目標探測定位的算法處理。同時還充分利用了cpld的邏輯控制功能和mcu豐富的外設資源,并設計出了dsp算法和中斷服務程序流程。該系統已經調試完成,并進行了充分的外場試驗。結果表明,系統工作穩定,各項指標基本達到了要求。

評論