一種實(shí)用的VXI總線寄存器基接口電路的設(shè)計(jì)

vxi(vmebus extention for instrumentation)總線是一種完全開放的、適用于各儀器生產(chǎn)廠家的模塊化儀器背板總線規(guī)范。它具有高速數(shù)據(jù)傳輸、結(jié)構(gòu)緊湊、配置靈活、電磁兼容性好等優(yōu)點(diǎn),已成為高性能測試系統(tǒng)集成的首選總線。vxi總線器件主要分為:寄存器基器件、消息基器件和存儲(chǔ)器基器件。目前寄存器基器件在應(yīng)用中所占比例最大(約70%),其實(shí)現(xiàn)方法在遵守vme協(xié)議的前提下,根據(jù)實(shí)際需要各有不同。vxi接口電路用于實(shí)現(xiàn)器件的地址尋址、總線仲裁、中斷仲裁和數(shù)據(jù)交換等。設(shè)計(jì)vxi接口首先需明確尋址空間和數(shù)據(jù)線寬度,vxi器件尋址有a16/a24、a16/a32和a16三種。a16/a24尋址支持16m字節(jié)空間,a16/a32尋址支持4g字節(jié)空間,a16尋址支持64字節(jié)地址空間,但不論哪種尋址方式,a16尋址能力是不可缺的。本文設(shè)計(jì)的vxi寄存器基接口電路是a16尋址的,支持d8和d16數(shù)據(jù)線傳輸,有較寬的使用范圍。其接口電路原理框圖如圖1所示。

1 dtb及dtb仲裁

本文引用地址:http://www.104case.com/article/21318.htmdtb(數(shù)據(jù)傳輸總線)及dtb仲裁是vxi接口的核心,dtb主要包括:尋址總線、數(shù)據(jù)總線和控制總線。其主要任務(wù)是:①通過地址修改碼(am)決定尋址空間和數(shù)據(jù)傳輸方式。②通過ds0*、ds1*、lword*、a1控制數(shù)據(jù)總線的寬度。③通過總線仲裁決定總線優(yōu)先使用權(quán)。

vxi總線器件在a16(16位地址)尋址時(shí),有64字節(jié)的地址空間,其呈部分作為器件配置寄存器地址(已具體指定),其余可用作用戶電路端口地址。每個(gè)器件的寄存器基地址由器件本身唯一的邏輯地址來確定。地址修改線在dtb周期中允許主模塊將附加的器件工作模式信息傳遞給從模塊。地址修改碼(am)共有64種,可分為三類:已定義修改碼、保留修改碼和用戶自定義碼。在已定義的地址修改碼中又分為三種:①短地址am碼,使用a02~a15地址線;②標(biāo)準(zhǔn)地址am碼,使用a02~a23地址線;③擴(kuò)展地址am碼,使用a02~a31地址線。a16短地址尋址主要是用來尋址器件i/o端口,其地址修改碼為:29h、2dh。

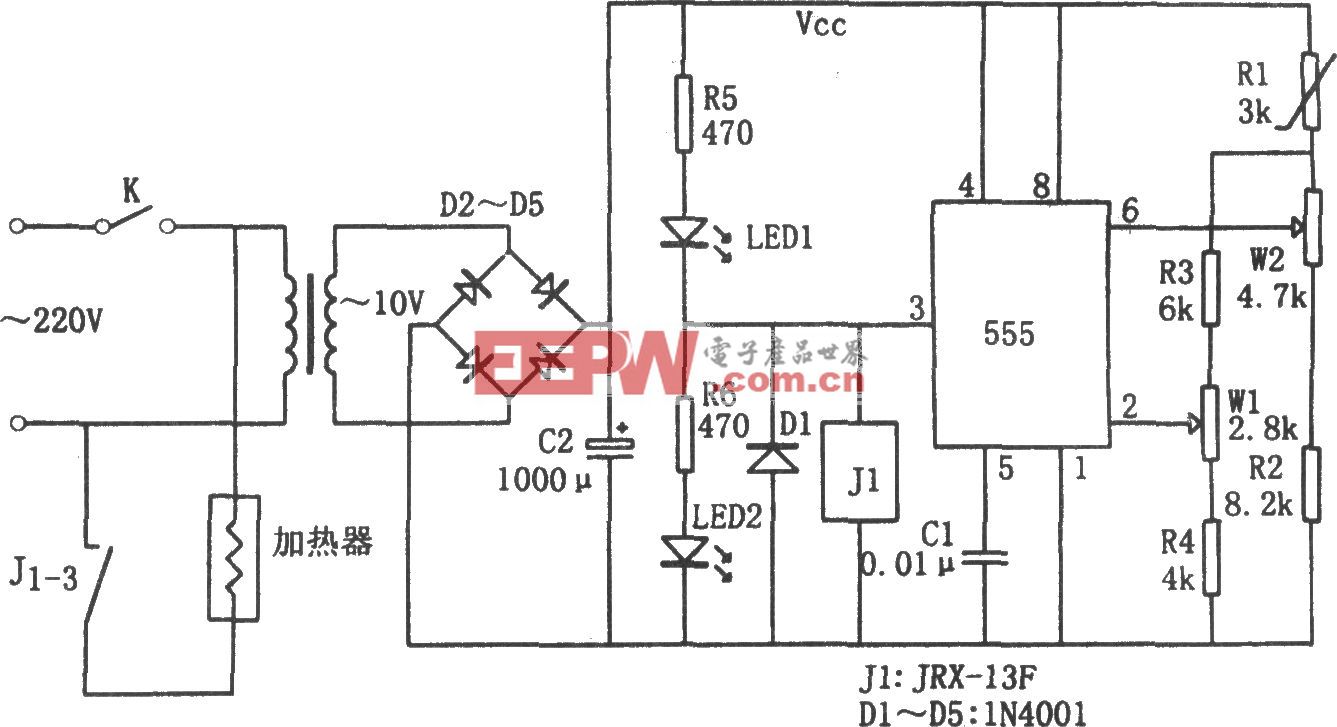

圖2為vxi器件尋址電路圖,其中u1為可編程邏輯器件,其表達(dá)式為:vxiena*=as*+!iack*a14+!a15+!am5+am4+!am3+am1+!am0;(!iack*表示系統(tǒng)無中斷請(qǐng)求)。尋址過程為:當(dāng)vxi主模塊發(fā)出的地址修改碼對(duì)應(yīng)為29或2d、總線上地址a6~a13和邏輯地址設(shè)置開關(guān)k1的設(shè)置相同并且地址允許線as有效時(shí),圖2中的myvxiena*有效(為低),表示本器件允許被vxi系統(tǒng)尋址。在允許本器件尋址的基礎(chǔ)上(即myvxiena*有效),再通過myvxiena*、a1~a5、lword*、ds0*、ds1*譯碼生成64字節(jié)地址,根據(jù)vme總線協(xié)議可譯出單字節(jié)地址和雙字節(jié)地址。協(xié)議協(xié)定:當(dāng)單字節(jié)讀寫時(shí),奇地址ds0*為低、ds1*為高,偶地址ds1*為低、ds0*為高,lword*為高;雙字節(jié)讀寫時(shí),ds0*和ds1*為低、lwodr*為高;四字節(jié)讀寫時(shí),ds0*、ds1*和lword*都為低。

dtb數(shù)據(jù)傳輸應(yīng)答主要依賴dtack*和ds0*之間的互鎖性握手關(guān)系,而與數(shù)據(jù)線上有效數(shù)據(jù)什么時(shí)候出現(xiàn)無關(guān),所以單次讀寫操作的速度完全決定應(yīng)答過程。為適應(yīng)不同速度用戶端口讀寫數(shù)據(jù)的可靠性,本文采用由用戶端口數(shù)據(jù)準(zhǔn)備好線(datready*)去同步dtack*答應(yīng)速度的方法來保證數(shù)據(jù)傳輸?shù)挠行浴T摲椒ǖ膬?yōu)點(diǎn)是電路簡單、使用方便,缺點(diǎn)是占用dtb時(shí)間長,影響vxi系統(tǒng)性能,且最長延時(shí)時(shí)間不得超過20μs。通常情況下用戶可通過數(shù)據(jù)暫存的方法實(shí)現(xiàn)數(shù)據(jù)可靠傳輸,并使用戶端口數(shù)據(jù)準(zhǔn)備好線(datready*)接地。由于寄存器基器件在vxi系統(tǒng)中只能作為從模塊使用,所以其總線請(qǐng)求只有該器件發(fā)生中斷請(qǐng)求時(shí)才由中斷管理模塊提出。

2 中斷請(qǐng)求及仲裁電路

vxi系統(tǒng)設(shè)有七級(jí)中斷,優(yōu)先中斷部遲疑不決包括:①中斷請(qǐng)求線irq1*~irq7*;②中斷應(yīng)答線iack*;③中斷應(yīng)答輸入線iackin*;④中斷應(yīng)答輸出線iackout*。從系統(tǒng)的角度看,在vxi系統(tǒng)中有一個(gè)成菊花鏈的中斷查詢系統(tǒng)。當(dāng)vxi系統(tǒng)中有中斷請(qǐng)求時(shí),中怕管理器使中斷應(yīng)答信號(hào)iack*有效(置低),并送往菊花鏈驅(qū)動(dòng)器,菊花鏈驅(qū)動(dòng)器使輸出iackout*有效,送至相鄰的下一個(gè)器件。如果相鄰器件沒有中斷請(qǐng)求,則該器件的iackout*輸出仍為低,繼續(xù)向下一個(gè)相鄰器件傳送;當(dāng)此器件有中斷請(qǐng)求時(shí),所以其輸出iackout*為高,進(jìn)入中斷過程,并屏蔽后級(jí)器件的中斷應(yīng)答。

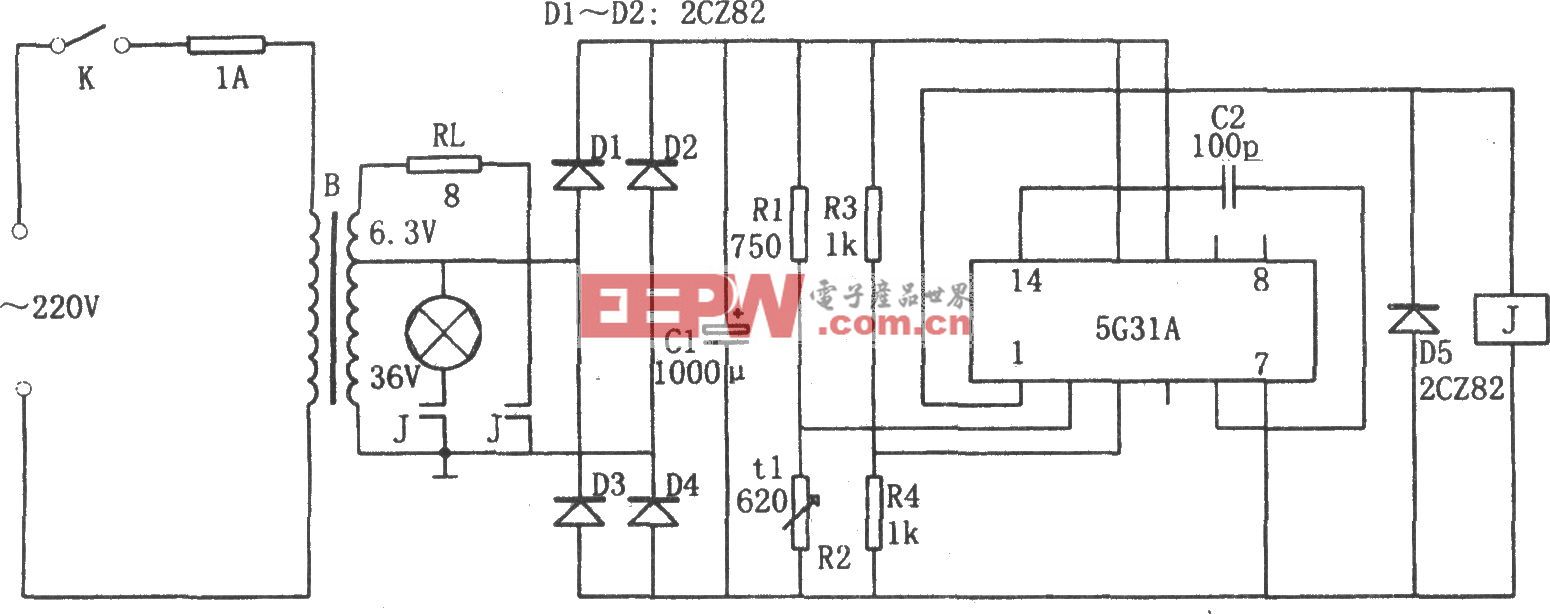

為實(shí)現(xiàn)中斷請(qǐng)求和中斷仲裁,每個(gè)器件的中斷仲裁電路應(yīng)完成的功能為:①產(chǎn)生中斷請(qǐng)求;②上傳狀態(tài)/識(shí)別碼;③屏蔽后級(jí)中斷應(yīng)答。本文設(shè)計(jì)的中斷仲裁電路如圖3所示。其中tx1~tx3來自中斷號(hào)選擇跳線器,inner-irq為器件內(nèi)部用戶電路中斷請(qǐng)求信號(hào),上升沿有效。中斷請(qǐng)求過程分如下四步:(1)在系統(tǒng)復(fù)位或中斷復(fù)位(來自控制寄存器)后,irqopen*為“1”使比較電路輸出“1”,使中斷應(yīng)答菊花鏈暢通,且譯碼電路不工作。(2)當(dāng)本器件內(nèi)有中斷請(qǐng)求時(shí),使irqopen*為“0”,則譯碼電路根據(jù)中斷置位開關(guān)的設(shè)置輸出相應(yīng)中斷請(qǐng)求信號(hào)irqx *。當(dāng)中斷管理器接收中斷請(qǐng)求信號(hào)后使iack*有效,并送往中斷菊花鏈驅(qū)動(dòng)器使之輸出iackout*有效,同時(shí)中斷管理器請(qǐng)求dtb總線使用權(quán)。(3)當(dāng)中斷管理器獲得dtb使用權(quán)后,根據(jù)接收到的中斷請(qǐng)求信號(hào),在地址允許線as+作用下在地址線上輸出相應(yīng)的a1~a3地址,使比較器輸出“0”,從而使iackout*變高,屏蔽后續(xù)中斷,并清除本器件內(nèi)部中斷請(qǐng)求。(4)中斷管理器使數(shù)據(jù)允許信號(hào)ds0*為低,讀出器件狀態(tài)/識(shí)別碼,響應(yīng)中斷,同時(shí)在ds0*的上升沿清除中斷請(qǐng)求(使irqopen*為“1”),接通中斷應(yīng)答菊花鏈,進(jìn)入中斷過程。

3 可編程器件實(shí)現(xiàn)和調(diào)試

為了克服用中小規(guī)模集成電路實(shí)現(xiàn)vxi接口電路存在的體積大、可靠性差和可調(diào)試性差等不足,可采用可編程器件實(shí)現(xiàn)接口電路。本文采用的器件是altera公司的max系列,采用的器件可編程軟件平臺(tái)的max+plusii。max+plus ii在編程上提供了多種電路描述形式,主要有圖形描述、ahdl描述和vhdl描述等。本文采用圖形描述和ahdl描述相結(jié)合的描述方法。接口電路的主框架結(jié)構(gòu)和能夠用標(biāo)準(zhǔn)元件表述的子模塊電路用圖形描述方法設(shè)計(jì),部分功能子模塊用ahdl語言描述。這種設(shè)計(jì)方式的電路原理結(jié)構(gòu)直觀、功能描述簡潔。vxi接口電路硬件描述子程序模塊由地址修改碼器件尋址、端口地址譯碼、中斷請(qǐng)求及控制、寄存器配置四部分組成。

在vxi器件中,寄存器配置步驟是必不可少的,vxi寄存器基器件主要配置寄存器有:識(shí)別/邏輯地址寄存器、器件類型寄存、狀態(tài)/控制寄存器。在接口電路的性質(zhì)特性明確的前提下,寄存器基器件的配置是確定的,所以直接在可編程器件中實(shí)現(xiàn),且更改也很方便。以下列出的是vxi寄存器基接口電路的主要邏輯表達(dá)式(用ahdl語言格式):

vxiena=as#!iack#!a14#!a15#!am5#am4#!am3#am1#!am0;

myvxiena=vxiena#(a6$q0)#(a7$q1)#(a8$q2)#(a9$q3)#(a10$q4)#(a11$q5)#(a12$q6)#(a13$q7);

acked=(tx1$a1)#(tx2$a2)#(tx3$a3)#iack#!sysrst#!irqpend#as#iackin;

dtacknode=!(ds0&ds1#myvxiena&acked);

drack=dff(dtaknode,sysclk,vcc,vcc);

ioena=myvxiena#ds0&ds0&ds1#!lword;

iackout=as#iackin#!ack;

需要注意的是,在使用中由于部分信號(hào)線與vxi背板總線連接時(shí)需要采用集電極開路方式接入,如dtack*、sysfail*、brx*等,所以應(yīng)增加一級(jí)集電極開路門電路后再與vxi背板總線連接。

接口電路調(diào)試有兩種方式,一是利用labwindow/vci開發(fā)工具預(yù)先編好一個(gè)帶操作軟面板的調(diào)試程序,它包含有各項(xiàng)功能調(diào)試控件和相關(guān)信息顯示窗。在調(diào)試電路時(shí)只需根據(jù)提示在軟面板上操作,就可及時(shí)得到信息顯示。這種調(diào)試電路方法方便、直觀,但由于調(diào)試程序的封裝會(huì)使得調(diào)試細(xì)節(jié)不透明。另一種形式是在ni公司提供的vxi資源管理器中對(duì)端口電路進(jìn)行操作、調(diào)試。這種方法是硬件開發(fā)人員主要采用的形式。主要過程為:先打開t&m explore對(duì)vxi系統(tǒng)初始化;啟動(dòng)vxi系統(tǒng)初始化;啟動(dòng)vxi interactive control面板,在bus access中通過修改偏移地址(offset)、輸出值(value)和觀察輸入值來對(duì)接口電路進(jìn)行調(diào)試。在調(diào)試過程中,為便于數(shù)據(jù)或波形的穩(wěn)定測試、觀察,一般將輸出數(shù)據(jù)的循環(huán)次數(shù)(count)設(shè)成一個(gè)較大數(shù)。這種調(diào)試方式雖然不很直觀,但卻非常靈活,容易發(fā)現(xiàn)硬件電路細(xì)節(jié)不足。

在vxi接口電路設(shè)計(jì)方面,只要遵循vxi總線協(xié)議,其具體實(shí)現(xiàn)方法多種多樣。本文從vxi總線協(xié)議出發(fā)詳細(xì)闡述了一種vxi寄存器基接口電路的設(shè)計(jì)方法和工作原理,并介紹了可編程器件實(shí)現(xiàn)方法和調(diào)試方法。用可編程電路使vxi接口電路模塊化、格式化,可縮短vxi總線器件的研制周期、縮小器件體積,提高器件的可靠性。該接口電路已在vxi數(shù)字i/o、vxi特征分析儀中使用。隨著儀器儀表技術(shù)、虛擬儀器技術(shù)的

發(fā)展,vxi總線作為高性能測試系統(tǒng)儀器的背板總線,將在航空航天、雷達(dá)、通訊等領(lǐng)域的測試中占據(jù)越來越重要的地位,開發(fā)高性能vxi總線器件是目前較熱門的研究方向。

評(píng)論