基于AD6623的多路中頻數字化直擴通信系統

擴頻通信具有抗干擾、抗多徑、低截獲概率等優點。20世紀70年代以來,擴頻通信的理論和方法得到了很大發展。直接序列擴頻(直擴)作為擴頻通信的一種常用方式,已成功地應用于軍事和民用通信中,并已成為第三代移動通信系統的核心技術之一,充分顯示了其顯著優點和強大生命力。

擴頻通信是以增加信息傳輸的帶寬為代價的。而現有的頻帶資源非常有限,為了提高單位帶寬內信息傳輸的速率,筆者提出采用直接序列擴頻cdma思想。在發端,將一路串行的數據信息經串/并轉換轉換為n路并行的數據信息,然后分別用n個相互正交的pn碼對每路信息進行調制完成擴頻,形成n路擴頻的基帶信息,每路基帶信息再經過基帶成形濾波,上變頻調制到同一中頻后再將n路信號合成送給射頻接口完成發送。在收端,用與發端相同的n個pn碼分別與接收信號進行互相關運算,然后與判決門限比較獲取同步信息,比較互相關值大小獲得用戶數據,將恢復的n路數據再進行并/串轉換即恢復出原始發送信息。這樣,整個系統所需的傳輸帶寬就降低為原來的1/n。

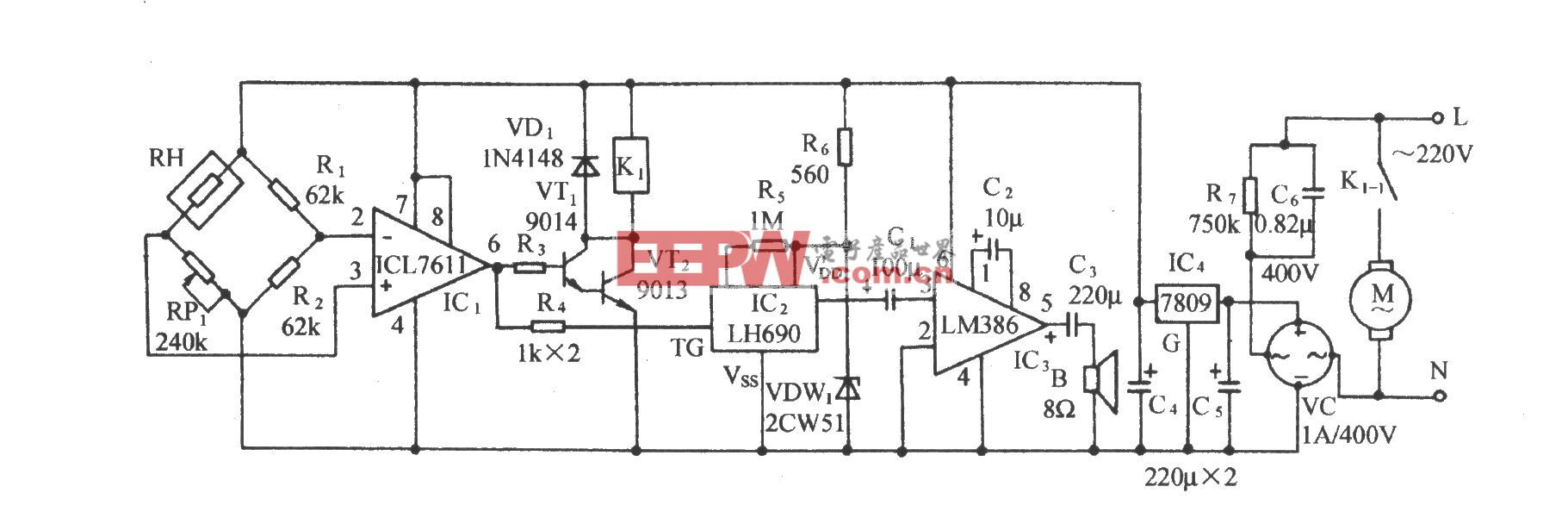

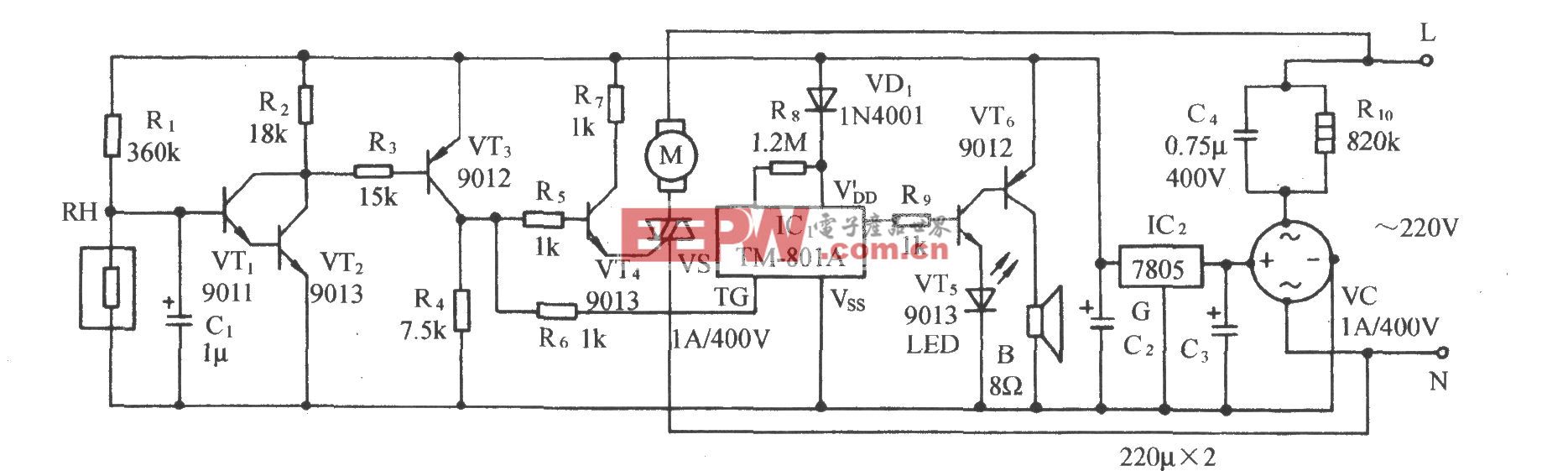

多路中頻數字化直擴系統的原理示意圖如圖1所示。

1 多路中頻數字化直擴通信系統的總體設計

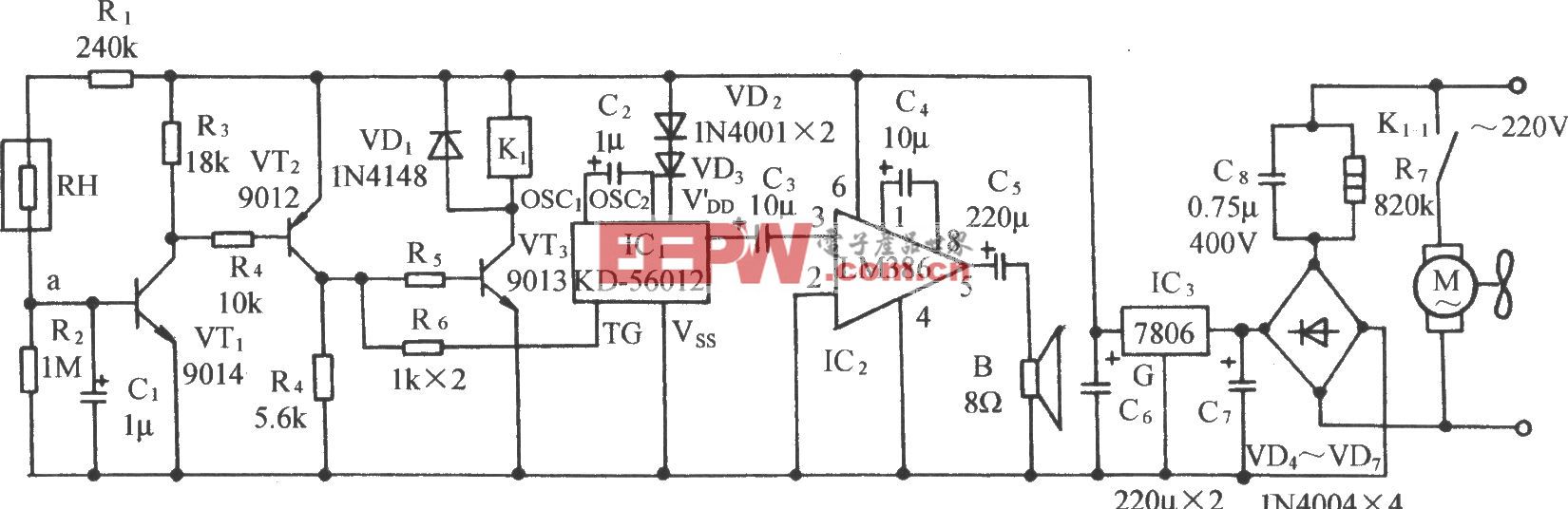

系統硬件電路設計框圖如圖2所示。

a/d轉換器采用ad公司的ad6644,它的最高采樣率可達65msps,分辨率為14位。在本系統中,由ad6644直接對6mhz中頻信號進行過采樣,實現系統的中頻數字化,采樣時鐘為19.6608mhz。

數字下變頻器選用ad公司的ad6620,它是美國ad公司推出的高性能數字信號處理芯片,可以完成高速數字信號的下變頻及抽取濾波工作,功能強大。內部信號處理單元由四個部分組成:頻率變換器、二階固定系數梳狀抽取濾波器(cic2)、五階固定系數梳狀抽取濾波器(cic5)和一個系數可編程的抽取濾波器(rcf)。在本系統中,ad6620的初始化由dsp

tms320lc31完成,ad6620通過并口向dsp輸出處理后的基帶數據。

d/a轉換器采用ad公司的ad9772a,它的最高轉換速率為160mhz,轉換位數為14位。在本系統中,由ad9772a完成發射單元的多路合成數字中頻向模擬中頻的轉換,轉換時鐘頻率為19.6608mhz。

數字上變頻器采用ad公司的ad6623,其主要特征有以下幾點:高達104mhz的工作時鐘、單片集成四個獨立的數字發射通道、可編程插值濾波器和增益控制。ad6623內部的信號處理包括以下四個部分:頻率變換器、二階重插值級聯積分梳狀濾波器(rcic2)、五階插值級聯積分梳狀濾波器(cic5)以及一個ram系數濾波器(rcf)。在本系統中共采用四片ad6623組成16路直接序列擴頻發射單元,每一路分別從fpga處取得擴頻基帶信息,進行基帶成形濾波、插值和上變頻調制到6mhz的中頻,最后將16路中頻調制信號合成為一路,再經d/a轉換后送給射頻發射單元接口。

dsp采用ti公司的tms320lc31。tms320lc31采用改進的哈佛結構,是一種能進行浮點運算的數字信號處理芯片,主頻可達60mhz。在本系統中,tms320lc31主要完成的功能是:在發射過程中,由程序產生模擬的基帶信息,當dsp檢測到fpga產生的申請數據的中斷信號時就將模擬基帶信息通過數據總線送給fpga;在接收過程中,dsp通過fpga產生的中斷信號分別對已完成解擴的各路數據進行接收,完成各路信息的解調,并將解調出的各路信息進行并串轉換還原為發射時的一路串行信息。此外,dsp在系統上電時負責完成ad6623和ad6620的初始化,在運行過程中,還要負責ad6620的載波恢復。

fpga采用的是altera公司的ep1s40b956c7,它內部含有41250個邏輯單元,可用的i/o管腳為683個,速度為0.7ns,完全可以滿足系統的各項性能要求。在本系統的發射過程中,由fpga向dsp發中斷申請,獲得待發送的基帶信息。在fpga中,將一路串行的基帶信息轉換為16路并行的基帶信息,并分別與16個互相正交的pn碼相乘完成擴頻,然后分別送給四片ad6623的16個數據通道。在接收過程中,數字下變頻器ad6620將下變頻、濾波后的基帶數據送給fpga,分別與16個本地正交pn進行匹配,完成16路pn碼的捕獲跟蹤,從而實現16路數據的解擴。最后fpga向dsp發送中斷,由dsp完成16路數據的組裝還原。

2 關鍵技術

ad6623內集成了四個獨立的數字信號處理器(tsp),每個tsp由可編程內插系數濾波器(rcf)、可編程功率控制單元、可編程五階級聯積分梳狀濾波器(cic5)、二階重采樣級聯積分梳狀濾波器(rcic2)和一個數控振蕩器(nco)等五個級聯的信號處理單元組成。通過對這五個信號處理單元參數的不同設置,可以使系統以同一套硬件實現不同的功能。

2.1 nco頻率值的設定

ad6623的每一個通道都有一個獨立的調制器,它可以把從cic濾波器中接收的數據上變頻成數字中頻,并送入多載波合并單元。該調制器由一個32比特的正交nco和一個正交幅度混頻器(qam)組成,該數字中頻的計算公式如下:

式中,nco_ frequency是寫入寄存器oxn02中的值;fif是期望的中頻頻率; fnco是nco的頻率,在輸出是實數時是系統工作時鐘fclk的一半,而在輸出是復數時是fclk的四分之一。

在此系統中,輸出為實數模式,要求上變頻到fif為6mhz的數字中頻,系統工作時鐘fclk為19.6608mhz,帶入上式可求得nco_

frequency的十六進制表示為4e200000。

2.2 插值系數的的設定

在本系統中,ad6623的每個通道要將chip速率為614.4khz的擴頻信息插值到等于系統的工作時鐘頻率19.6608mhz,這樣總的插值系數為32(19.6608mhz/614.4khz)。利用ad公司提供的filter

design軟件可得到一組最佳的各級濾波器插值系數的分配方案:mcic2=1,lcic2=1,cic5=4,mrcf=8。

2.3 濾波器系數的設定

fir濾波器的設計目標是讓614.4khz的低通目標信號盡可能地通過,并抑制帶外干擾。從濾波器幅頻特性曲線的角度來看,也就是要求通帶波動盡可能地小,通帶寬度盡可能地與信號帶寬相等,過渡帶盡可能地銳利,阻帶衰減盡可能地大。通常,fir濾波器的階數越高,幅頻特性越好,ad6623提供的濾波器階數最高可達255階,具體選擇多少要根據實際情況而定。

在本系統中使用窗函數設計法(或稱傅立葉級數法)確定濾波器系數,即由理想的濾波器頻率響應hd(w)經傅立葉反變換導出hd(n),然后用一個有限長窗函數序列w(n)截取。由于輸入給可編程系數濾波器的數據經過了一次插值,且插值系數mrcf為8,因此此時輸入數據的采樣率fs為:

fs=614.4k×8=4.9152mhz

因為截止頻率fc為614.4khz,所以數字域截止頻率wc為:

這表明在通帶|w|≤wc范圍內,hd(ejw)的幅度是均勻的,且其值為1、相位為-wα。

由此可得:

取w(n)=rn(n),按照線性相位濾波器的約束,h(n)必須為偶對稱,對稱中心長度應為長度的一半(n-1)/2,且α=(n-1)/2,取n=255,則α=127。于是可得濾波器的系數為:

fir濾波器的幅頻響應曲線如圖3所示。

2.4 載波合并單元

ad6623的載波合并單元用來合并各信道的輸出以產生多載波信號,該結果與18比特寬帶輸入總線上的內容相加后,將在高速時鐘的上升沿送至18比特寬帶輸出總線。

3 實驗驗證

在基于圖2的硬件平臺下,dsp將模擬速率為307.2kbps的基帶信息序列送給fpga作為發送信息序列,經串/并轉換后每路信息速率降低為19.2kbps,

pn碼長為32,所以擴頻后每路chip速率為614.4kbps。在發射端,發送信息序列經fpga擴頻調制后送給ad6623上變頻,然后送給ad9772a完成d/a變換;在接收端,中頻信號經過ad6644采樣和ad6620下變頻后,再經fpga解擴和dsp檢測,解調出的信息經計算機串口送給計算機顯示器顯示解調結果。經實際電路驗證,dsp能正確解調出所發送的擴頻信號。證明利用ad6623等所設計的中頻數字化多路直接序列擴頻通信系統,具有硬件設計靈活、資源消耗少、調試修改方便等優點,對軟件進行一定的修改,則可以作為一種通用的多路中頻數字化直擴通信系統處理平臺。

基于ad6623的多路中頻數字化直接序列擴頻通信系統,可以方便地改變系統的調制方式和調制頻率,而且還可以適應不同信息速率和各種偽碼碼長的直接序列擴頻通信,關鍵一點在于它采用了碼分多址的思想,使得帶寬利用率大大提高。實驗測試表明:系統效果良好,控制靈活,適應范圍廣,具有較好的應用前景。

評論