基于FPGA的小數分頻器的實現

頻率合成技術是現代通訊系統的重要組成部分,他將一個高穩定和高準確度的基準頻率,經過四則運算,產生同樣穩定度和基準度的頻率。分頻器是集成電路中最基礎也是最常用的電路。整數分頻器的實現比較簡單,可采用標準的計數器或可編程邏輯器件設計實現。但在某些場合下,時鐘源與所需的頻率不成整數倍關系,此時可采用小數分頻器進行分頻。本文利用veriloghdl硬件描述語言的設計方式,通過modelsimse開發軟件進行仿真,設計基于fpga的雙模前置小數分頻器。隨著超大規模集成電路的發展,利用fpga小數分頻合成技術解決了單環數字頻率合成器中高鑒相頻率與小頻間隔之間的矛盾。

1雙模前置小數分頻原理

本文引用地址:http://www.104case.com/article/21095.htm小數分頻器的實現方法很多,但其基本原理一樣,即在若干個分頻周期中采取某種方法使某幾個周期多計或少計一個數,從而在整個計數周期的總體平均意義上獲得一個小數分頻比,設要進行分頻比為k的小數分頻,k可表示為:

式中:n,n,x均為正整數;n為到x的位數,即k有n位小數。另一方面,分頻比又可以寫成:

式中:m為分頻器輸入脈沖數;p為輸出脈沖數。

令p=10n,則:

以上是小數分頻器的一種實現方法,即在進行10n次n分頻時,設法多輸入x個脈沖。

2電路組成

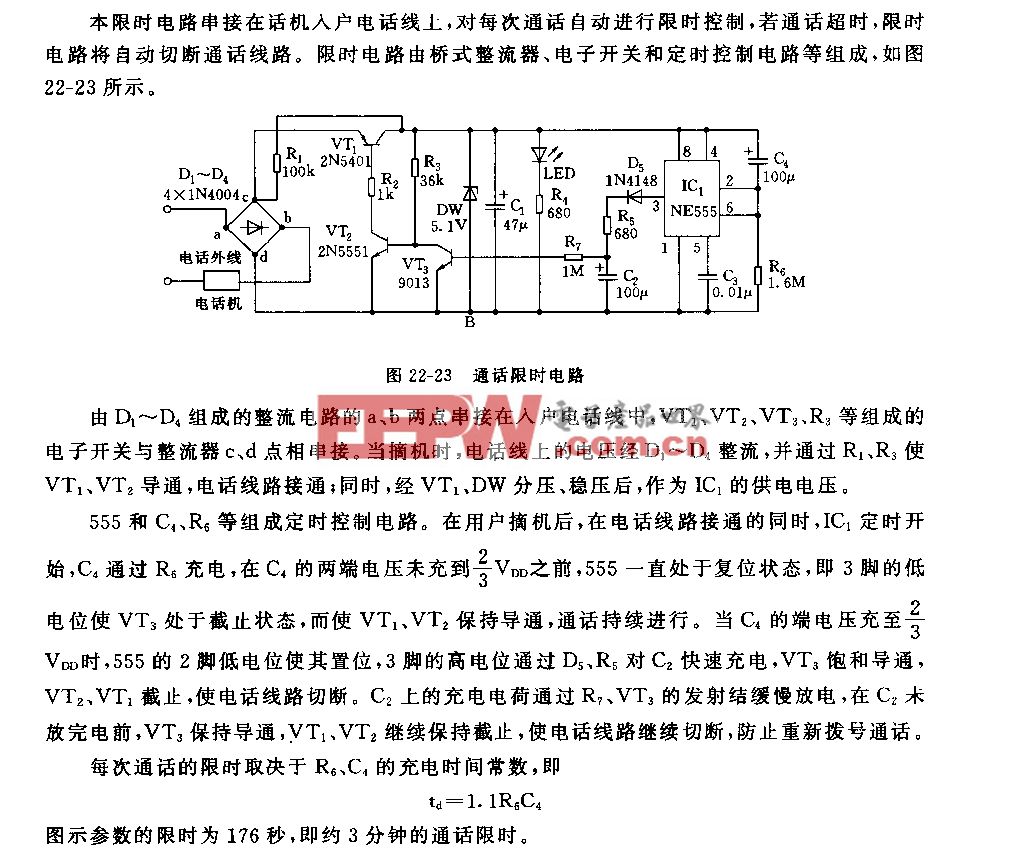

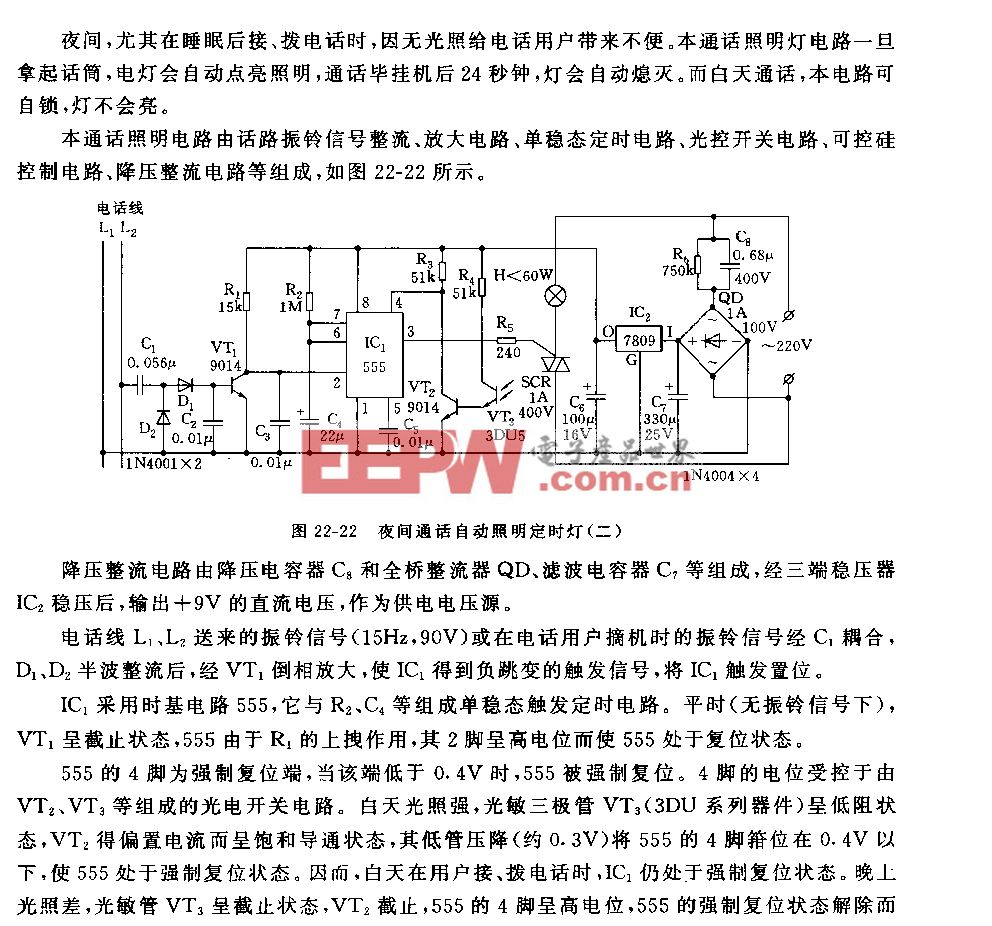

每個周期分頻n+10-n.x,其電路雙模前置小數分頻器電路由÷n/n+1雙模分頻器、控制計數器和控制邏輯3部分組成。當a點電平為1時,進行÷n分頻;當a點電平為0時進行÷n+1分頻。適當設計控制邏輯,使在10n個分頻周期中分頻器有x次進行÷n+1分頻,這樣,當從fo輸出10n個脈沖時,在fi處輸入了x.(n+1)+(10n-x).n個脈沖,也就是10n.n+x個脈沖,其原理如圖1所示。

3小數分頻器的verilog-hdl設計

現通?過設計一個分頻系數為8.7的分頻器來給出使用veriloghdl語言設計數字邏輯電路的一般設計方法。這里使用÷8/9雙模前置分頻器,按照前面的分析,可以通過計數器計數先做3次8分頻,后做7次9分頻,即可得到平均分頻系數8.7。由于從n分頻切換到n+1分頻和從n+1分頻切換到n分頻都會產生一個隨時間增長的相位移,如果簡單的先進行3次8分頻后做7次9分頻將會產生很大的相位波動。考慮到該小數分頻器要進行多次8分頻和9分頻,那么就設法將兩種分頻混合均勻,這種“均勻”工作是通過計數器來完成的,在這里只討論一位小數的情況,下面簡要介紹這種混合的方法:

每進行一次分頻,計數值為10減去分頻系數的小數部分,各次計數值累加。若累加結果小于10,則進行n+1分頻,若大于10或等于10,則進行n分頻。該例中計數值為(10-7)=3,前3次累加結果都小于10,所以為9分頻,第四次累加結果為12,則去掉十位數后累加結果變為2,同時進行8分頻,表1給出了該分頻器的分頻過程。

若分頻系數后為兩位小數,則用100減去分頻系數的小數部分。用veriloghdl設計÷8/9雙模前置分頻器的描述程序如下:

4波形仿真

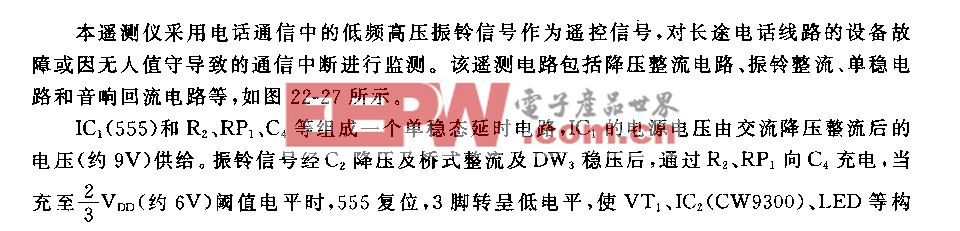

上述的÷8/9雙模前置分頻器的描述程序經modelsim編譯、時序模擬后,得到的波形如圖2所示。

由圖2可見,當reset為0時,分頻器復位,當a為1時,進行8分頻,當a為0時則進行9分頻。

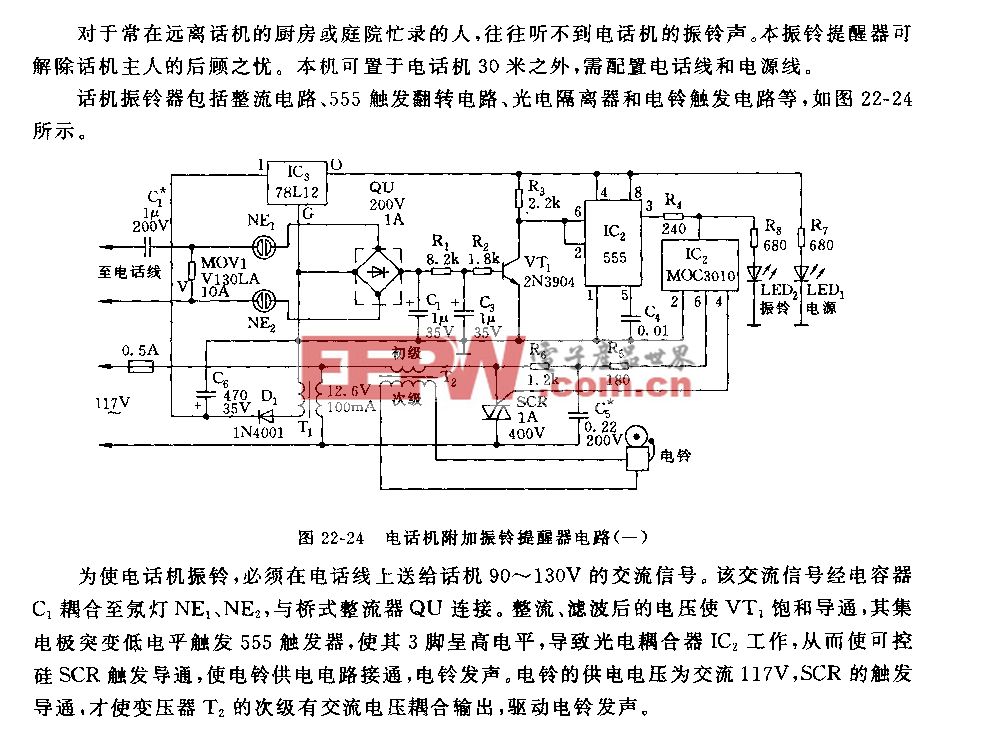

如圖3所示,在前3個時鐘,a值為0,則進行9分頻,其后一個時鐘a為1,進行8分頻,后兩個脈沖,又進行9分頻,后進行一次8分頻,然后又進行兩次9分頻,最后進行一次8分頻。

5電路實現

fpga現場可編程門陣列(fieldprogrammablegatearray)是20世紀80年代中期出現的高密度可編程邏輯器件。fpga及其軟件系統是開發數字電路的最新技術。他利用eda技術,以電路原理圖、硬件描述語言、狀態機等形式輸入設計邏輯;他提供功能模擬、時序仿真等模擬手段,在功能模擬和時序仿真度滿足要求后,經過一系列的變換,將輸入邏輯轉換成fpga器件的編程文件,以實現專用集成電路。本設計選用xilinx公司推出的90nm工藝制造的現場可編程門陳列spartan-3來設計小數分頻器,體積減小,可靠性提高。

6結語

采用前置雙頻分頻器設計的小數分頻器,小數分頻器的精度受控制計數器的影響,當n值為100時,小數分頻的精度達到1/100;當n值為1000時,小數分頻的精度達到1/1000;依此類推。fpga有相當豐富的硬件資源,因此可以用fpga設計高精度的小數分頻器。采用fpga組成的數字頻率合成器,單環鑒相頻率達100mhz以上,分辨率可達10-6。這種小數分頻器得到了廣泛的應用,例如,對圖象采集系統中的行分頻和列分頻的設計,就可以應用本分頻器電路作為時鐘發生器。

評論