同步時(shí)序邏輯電路的分析方法

內(nèi)容提要

7.1 概述

一、時(shí)序電路的定義

二、電路構(gòu)成

三、分類:

1 同步

2 異步

7.2 時(shí)序邏輯電路的分析方法

7.2.1 同步時(shí)序邏輯電路的分析方法

一、基本分析步驟

1.寫方程式

2.列狀態(tài)轉(zhuǎn)換真值表

3.邏輯功能的說明

4 畫狀態(tài)轉(zhuǎn)換圖和時(shí)序圖

二、分析舉例

[例7.2.1]

1.寫方程式

2.列狀態(tài)轉(zhuǎn)換真值表

3.邏輯功能的說明

4 畫狀態(tài)轉(zhuǎn)換圖和時(shí)序圖

5.檢查電路能否自啟動

[例7.2.2]

1.寫方程式

2.列狀態(tài)轉(zhuǎn)換真值表

3.邏輯功能的說明

4 畫狀態(tài)轉(zhuǎn)換圖和時(shí)序圖

7.2.2 異步時(shí)序邏輯電路的分析方法

應(yīng)寫出時(shí)鐘方程。

[例7.2.3]

1.寫方程式

2.列狀態(tài)轉(zhuǎn)換真值表

3.邏輯功能的說明

4 畫狀態(tài)轉(zhuǎn)換圖和時(shí)序圖

第7章 時(shí)序邏輯電路

內(nèi)容提要

時(shí)序邏輯電路的分析方法

異步計(jì)數(shù)器、同步計(jì)數(shù)器、寄存器與移位寄存器的基本工作原理

中規(guī)模集成電路的邏輯功能、使用方法和應(yīng)用

時(shí)序邏輯電路的設(shè)計(jì)方法

7.1 概述

一、定義:時(shí)序邏輯電路(又稱時(shí)序電路):在任何一個(gè)時(shí)刻的輸出狀態(tài)不僅取決于當(dāng)時(shí)的輸入信號,而且還取決于電路原來的狀態(tài)。

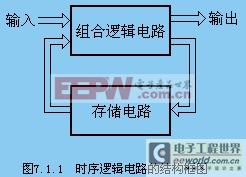

二、電路構(gòu)成:

存儲電路(主要是觸發(fā)器,且必不可少)+組合邏輯電路(可選)。

時(shí)序邏輯電路的狀態(tài)是由存儲電路來記憶和表示的。

三、分類

根據(jù)電路狀態(tài)轉(zhuǎn)換情況的不同分為:

1.同步時(shí)序邏輯電路:

所有觸發(fā)器的時(shí)鐘輸入端CP都連在一起,在同一個(gè)時(shí)鐘脈沖 CP作用下,凡具備翻轉(zhuǎn)條件的觸發(fā)器在同一時(shí)刻狀態(tài)翻轉(zhuǎn)。觸發(fā)器狀態(tài)的更新和時(shí)鐘脈沖CP是同步的。

2.異步時(shí)序邏輯電路

時(shí)鐘脈沖CP只接部分觸發(fā)器的時(shí)鐘輸入端,其余觸發(fā)器則由電路內(nèi)部信號觸發(fā)。因此,凡具備翻轉(zhuǎn)條件的觸發(fā)器狀態(tài)的翻轉(zhuǎn)有先有后,并不都和時(shí)鐘脈沖CP同步。

計(jì)數(shù)器中,時(shí)鐘脈沖CP又稱為計(jì)數(shù)脈沖。

7.2 時(shí)序邏輯電路的分析方法

時(shí)序邏輯電路的分析:根據(jù)給定的電路,寫出它的方程、列出狀態(tài)轉(zhuǎn)換真值表、畫出狀態(tài)轉(zhuǎn)換圖和時(shí)序圖,而后分析出它的功能。

7.2.1 同步時(shí)序邏輯電路的分析方法

同步時(shí)序邏輯電路中,所有觸發(fā)器都由同一個(gè)時(shí)鐘脈沖信號CP來觸發(fā),都對應(yīng)相同的電平或邊沿狀態(tài)更新。所以,可以不考慮時(shí)鐘條件。

課堂討論:現(xiàn)態(tài)和次態(tài)的時(shí)間分割點(diǎn)?

一、基本分析步驟

1.寫方程式

(1)輸出方程。時(shí)序邏輯電路的輸出邏輯表達(dá)式,它通常為現(xiàn)態(tài)的函數(shù)。

(2)驅(qū)動方程。各觸發(fā)器輸入端的邏輯表達(dá)式。即J=?,K=?,D=?

(3)狀態(tài)方程。將驅(qū)動方程代入相應(yīng)觸發(fā)器的特性方程中,便得到該觸發(fā)器的次態(tài)方程。時(shí)序邏輯電路的狀態(tài)方程由各觸發(fā)器次態(tài)的邏輯表達(dá)式組成。

JK F/F和D F/F的特性方程?

2.列狀態(tài)轉(zhuǎn)換真值表

將外輸入信號和現(xiàn)態(tài)作為輸入,次態(tài)和輸出作為輸出,列出狀態(tài)轉(zhuǎn)換真值表。

觸發(fā)器的邏輯功能的表示方法有哪些?相互轉(zhuǎn)換?特別:與或式→真值表?

3.邏輯功能的說明

根據(jù)狀態(tài)轉(zhuǎn)換真值表來說明電路的邏輯功能。

4.畫狀態(tài)轉(zhuǎn)換圖和時(shí)序圖

狀態(tài)轉(zhuǎn)換圖:電路由現(xiàn)態(tài)轉(zhuǎn)換到次態(tài)的示意圖。

時(shí)序圖:在時(shí)鐘脈沖CP作用下,各觸發(fā)器狀態(tài)變化的波形圖。

二、分析舉例

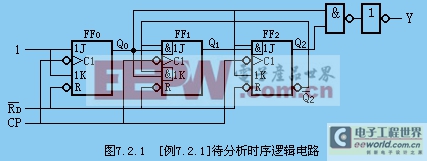

[例7.2.1] 試分析圖7.2.1所示電路的邏輯功能,并畫出狀態(tài)轉(zhuǎn)換圖和時(shí)序圖。

解:分析步驟

由電路可看出,時(shí)鐘脈沖CP加在每個(gè)觸發(fā)器的時(shí)鐘脈沖輸入端上。因此它是一個(gè)同步時(shí)序邏輯電路,時(shí)鐘方程可以不寫。

三個(gè)JK觸發(fā)器的狀態(tài)更新時(shí)刻都對應(yīng)CP的下降沿。

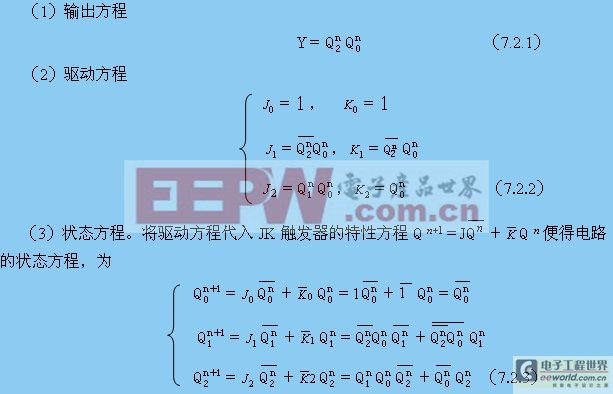

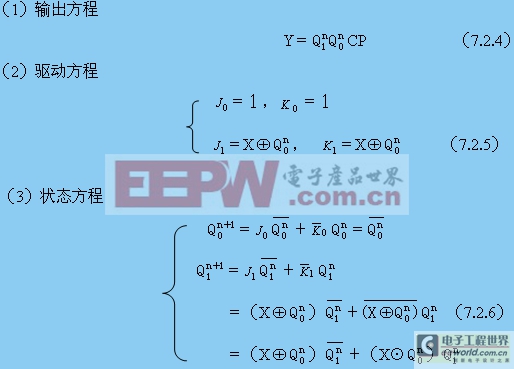

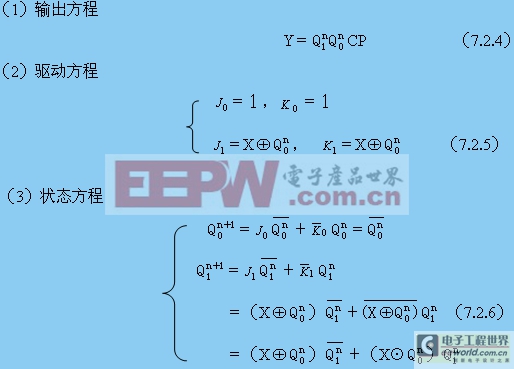

1.寫方程式

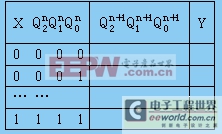

2.狀態(tài)轉(zhuǎn)換真值表

由狀態(tài)方程,可列狀態(tài)轉(zhuǎn)換真值表。

3.邏輯功能說明

由狀態(tài)轉(zhuǎn)換真值表,在輸入第6個(gè)計(jì)數(shù)脈沖CP后,返回原來的狀態(tài),同時(shí)輸出端Y輸出一個(gè)進(jìn)位脈沖。因此為同步六進(jìn)制計(jì)數(shù)器。

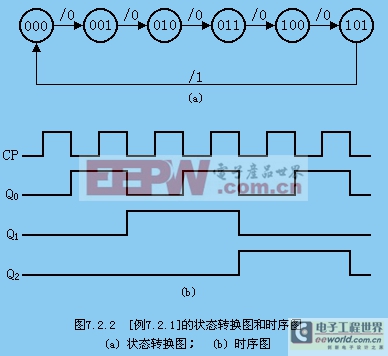

4.畫狀態(tài)轉(zhuǎn)換圖和時(shí)序圖

⑴ 根據(jù)狀態(tài)轉(zhuǎn)換真值表→狀態(tài)轉(zhuǎn)換圖。

圓圈內(nèi)表示電路的一個(gè)狀態(tài),

箭頭表示電路狀態(tài)的轉(zhuǎn)換方向(現(xiàn)態(tài)→次態(tài))

箭頭線上方標(biāo)注的X/Y為轉(zhuǎn)換條件,X為轉(zhuǎn)換前輸入變量的取值,Y為輸出值

由于本例沒有輸入變量,故X未標(biāo)上數(shù)值。

⑵ 根據(jù)狀態(tài)轉(zhuǎn)換真值表→時(shí)序圖(或稱工作波形圖)。

5.檢查電路能否自啟動

電路應(yīng)有![]() =8個(gè)工作狀態(tài),

=8個(gè)工作狀態(tài),

只有6個(gè)狀態(tài)被利用了,稱為有效狀態(tài)。

還有110和111沒有被利用,稱為無效狀態(tài)。

能夠自啟動:如果由于某種原因而進(jìn)入無效狀態(tài)工作時(shí),只要繼續(xù)輸入計(jì)數(shù)脈沖CP,電路會自動返回到有效狀態(tài)工作。

該電路能夠自啟動。

[例7.2.2] 試分析圖7.2.3所示電路的邏輯功能。并畫出狀態(tài)轉(zhuǎn)換圖和時(shí)序圖。

解:分析步驟

1.寫方程式

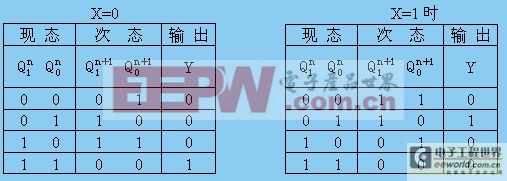

2.列狀態(tài)轉(zhuǎn)換真值表

由于輸入控制信號X可取0,也可取1,因此,應(yīng)分別列出X=0和X=1的兩張狀態(tài)轉(zhuǎn)換真值表。

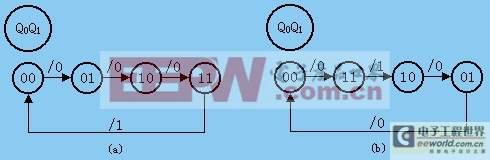

3.邏輯功能說明

在X=0時(shí),電路為加法計(jì)數(shù)器;

在X=1時(shí),電路為減法計(jì)數(shù)器。

因此,電路為同步四進(jìn)制加/減計(jì)數(shù)器。

4.畫狀態(tài)轉(zhuǎn)換圖和時(shí)序圖

可畫出X=0和X=1時(shí)的兩個(gè)狀態(tài)轉(zhuǎn)換圖。

如用一個(gè)狀態(tài)轉(zhuǎn)換圖時(shí),則應(yīng)在斜線上方標(biāo)明輸入變量X的取值。

畫時(shí)序圖。

7.2.2 異步時(shí)序邏輯電路的分析方法

在異步時(shí)序邏輯電路中,只有部分觸發(fā)器由計(jì)數(shù)脈沖信號源CP觸發(fā),而其它觸發(fā)器則由電路內(nèi)部信號觸發(fā)。

因此,應(yīng)考慮各個(gè)觸發(fā)器的時(shí)鐘條件,即應(yīng)寫出時(shí)鐘方程。

各個(gè)觸發(fā)器只有在滿足時(shí)鐘條件后,其狀態(tài)方程才能使用。否則,狀態(tài)保持不變。

這是異步時(shí)序邏輯電路在分析方法上和同步時(shí)序邏輯電路的根本不同點(diǎn)。

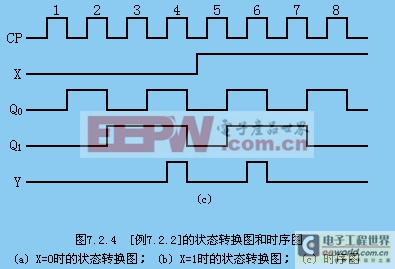

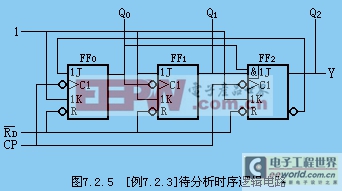

[例7.2.3] 試分析圖7.2.5所示電路的邏輯功能。并畫出狀態(tài)轉(zhuǎn)換圖和時(shí)序圖。

解:分析步驟

FF1的時(shí)鐘信號是由Q0端輸出的負(fù)躍變信號來觸發(fā)的,所以是異步時(shí)序邏輯電路。

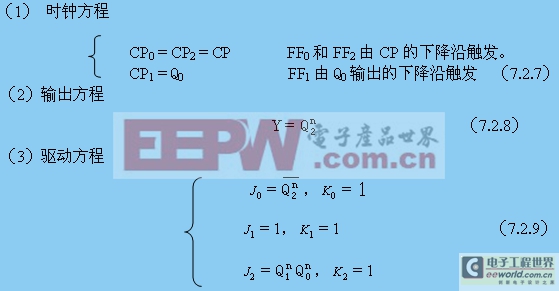

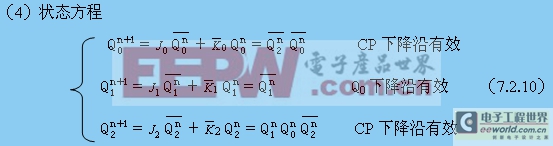

1.寫方程式

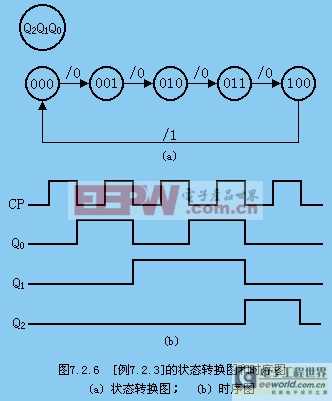

2.列狀態(tài)轉(zhuǎn)換真值表

狀態(tài)方程只有在滿足時(shí)鐘條件后才是有效的。否則將保持不變。

3.邏輯功能說明,

在輸入第5個(gè)計(jì)數(shù)脈沖時(shí),返回初始的000狀態(tài),同時(shí)Y輸出一個(gè)負(fù)躍變的進(jìn)位信號,因此,為五進(jìn)制計(jì)數(shù)器。

4.狀態(tài)轉(zhuǎn)換圖和時(shí)序圖

評論