基于FPGA的高速誤碼儀接收端設計方案的探討

引言

當今通信領域的發展日新月異,光纖和衛星通信已經成為主要的通信手段,通信容量越來越大,傳輸速率越來越高,因此,發展能夠檢測系統高速誤碼性能的誤碼儀就顯得十分重要。在高速誤碼儀的設計中,接收端的設計歷來是難點,本文將對這個問題進行探討,提出兩種可行的方案。

本文引用地址:http://www.104case.com/article/21000.htm1 高速誤碼儀接收端的主要功能和接口

1.1 主要功能

a)接收端能夠在fpga(現場可編程門陣列)芯片內部進行已知數據流(速率為3 00mbit?s-1/600 mbit?s-1)的比較以及錯誤統計;

b)能夠將統計結果在計算機中顯示;

c)能夠在計算機的控制下進行工作。

1.2 接口

a)高速接口。lvds串行輸入2路,并行輸入8路(與lvds輸入共用2路),usb輸出1路。

b)低速接口。lvttl/lvcmos(3.3 v)輸入共用一路9針串口,cmos/ttl(5 v)輸人共用一路9針串口。

c)時鐘接口(采用同軸電纜傳輸)。2路lvds輸入,1路ttl輸入。

2 高速誤碼儀接收端的設計方案

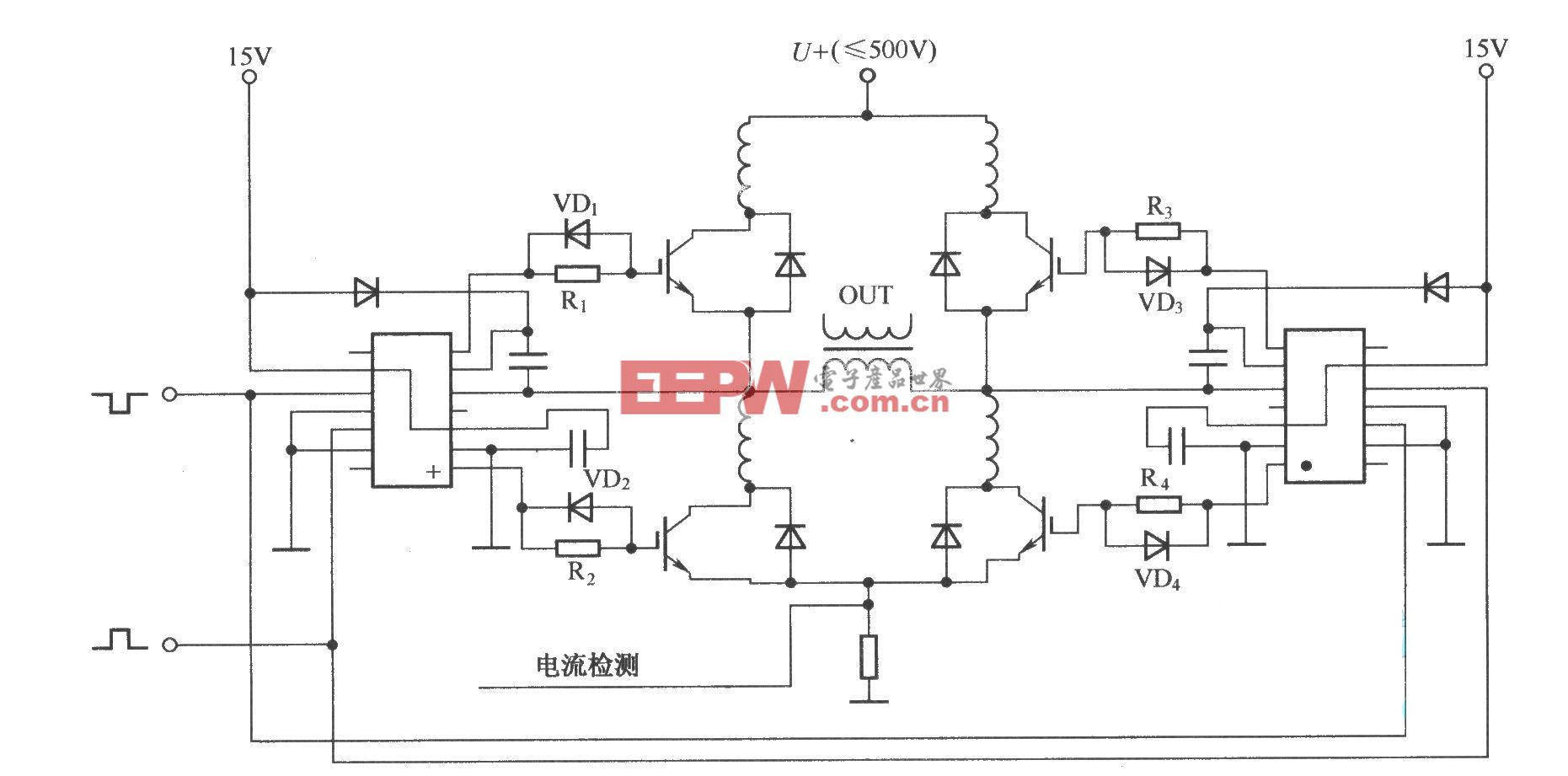

兩個方案中fpga以xilinx公司的virtex-ⅱ為例。

2.1 方案1

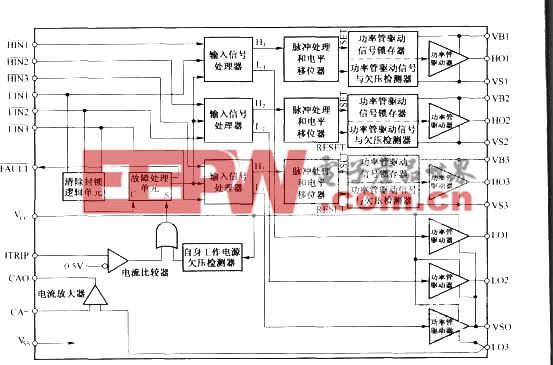

方案1系統框圖如圖1所示。

2.1.1 分接系統

分接系統1接收300 mbit?s-1/600mbit?s-1串行數據和時鐘,將其分成2路并行數據。分接系統2將已同步的2路并行數據分成16路并行數據。分接系統采用xilinx公司給的參考ipcore。不過,該ipcore是4路串行轉8路并行,需要將其轉換為1路串行轉2路并行和l路串行轉8路并行。

2.1.2 同步電路

同步電路如圖2所示。同步頭為31 bit,其中將16 bit最佳碼間隔1 bit插入,同步電路采用滑動同步法,即將分接后的2路并行數據存入2個16 bit的移位寄存器中,分別與預先存入ram中的16 bit同步頭進行比較(比較功能由比較器完成,即異或2組數據,結果為全0即為相等,其他則為不等)。

如果一致,在定時信號的控制下,后方保護計數器加1,當計數器的值為3時,視為已經同步,后方保護計數器清零,前方保護計數器開始工作,同步指示燈亮,將數據分接為16路并行數據送到比較器,當比較完1幀后,再與同步頭進行比較。如果一致,在定時信號的控制下,前方保護計數器不計數;如果不一致,前方保護計數器加1,如此循環,當前方保護計數器為3時,視為失步,同步指示燈滅,停止比較數據。

如果不一致,則等待下一個時鐘上升沿到來,再進行比較。

這樣分配同步頭是為了將并行檢測同步頭變為串行檢測同步頭,在2個16 bit的移位寄存器中,同步頭必定在其中一個移位寄存器的16 bit中。因此,只需同時檢測這2個移位寄存器的16 bit,即可判斷是否是同步頭。當在奇數移位寄存器檢測到同步頭時,從偶數移位寄存器的第16 bit和從奇數移位寄存器的輸入(17 bit,見圖3)輸出;當在偶數移位寄存器檢測到同步頭時,從奇數移位寄存器的輸入(17 bit,見圖3)和從偶數移位寄存器的輸入(17bit)輸出。它們的輸出在dcm的控制下分別分接為8路并行數據流,送到比較電路。同步頭的比較是將16 bit同步頭與待測數據按位異或,結果為全0時認為相等。如圖3所示。

2.1.3 比較電路

比較電路如圖4所示,用來判斷誤碼數,主要由異或電路、譯碼器、累加器和鎖存器組成。其信號流程為來自同步電路的16路并行數據在使能信號的控制下,與本地存儲器sram中的預存數據進行16位異或,將結果送到譯碼器中譯碼,這里的譯碼是計算16 bit數據中1的個數,然后將結果轉換為4位二進制數,譯碼器的輸出即為當前的誤碼數(二進制),送到累加器進行累加,將結果送到鎖存器鎖存,在控制信號的控制下將結果送到pc中轉換為十進制并顯示。

2.2 方案2

方案2系統框圖如圖5所示。

同步電路如圖6所示。同步頭采用16 bit最佳碼,串行數據接收到后先進入16 bit移位寄存器,并行輸出到比較器,與預制同步頭進行比較,前方保護計數器和后方保護計數器的流程同方案1,當確認同步后,將串行數據直接送到分接系統。

分接系統和比較電路同方案1。

2.3 2種方案的比較

從上述可以看出2種方案的特點。方案2原理較為簡單,在低速誤碼儀設計中比較常見,但由于本設計中要求的數據率較高,采用的fpga芯片又沒有集成串/并轉換硬件,因此,直接實現比較困難。目前,市場上已經有集成串/并轉換模塊的fpga出售,不過價格已經超出了預算。方案1的實現比較復雜,主要目的是先降低串行數據流的速率,再檢測同步頭,同時,這也增加了邏輯的復雜度,所以不宜將路數分得太多(分2路為宜)。其優點是可以最大限度地應用目前廉價的低速fpga芯片來實現所需的高速誤碼儀。

3 結束語

基于fpga芯片的高速誤碼儀設計具有很大的靈活性,可以很容易地進行改進;同時,芯片內部結構和制作工藝的進步會大大降低軟件設計的復雜度,也增強了系統的功能。考慮到成本的約束,設計并沒有采用更先進的fpga芯片,而是在實現原理上尋求變通,這也是科研中常用的辦法。

評論