邏輯分析儀原理及應用

·定時分析儀的觸發

邏輯分析儀連續捕獲數據,并在找到跟蹤點后停止采集。這樣,邏輯分析儀就能顯示出被稱為負時間的跟蹤點前的信息,以及跟蹤點后的信息。

碼型觸發

設置定時分析儀的跟蹤特性與設置示波器的觸發電平和斜率稍有一點區別。許多分析儀是在跨多條輸入線的高和低碼型上觸發。為使某些用戶更感方便,絕大多數分析儀的觸發點不僅可用二進制( 1 和 0),而且可用十六進制、八進制、ASCII或十進制設置。在查看4、 8、16、24、32bit寬的總線時,使用十六進制的觸發點會更加方便。設想如果用二進制設置24bit總線就會麻煩得多。

邊沿觸發

在調節示波器的觸發電平旋鈕時,您知道是在設置電壓比較器的電平,這個電平將告訴示波器在輸入電壓穿越該電平時觸發。定時分析儀的邊沿觸發與其基本相似,但觸發電平已預設置到邏輯閾值。大部分邏輯器件都與電平相關,這些器件的時鐘和控制信號通常都對邊沿敏感。邊沿觸發使您能與器件時鐘同步地捕獲數據。您能告訴分析儀在時鐘邊沿產生(上升或下降)時捕獲數據,并獲取移位寄存器的所有輸出。當然在這種情況下,必須延遲跟蹤點,以顧及通過移位寄存器的傳播延遲。

狀態分析儀基礎

如果您從未使用過狀態分析儀,您可能認為這是一種極為復雜的儀器,需要花很多時間才能掌握使用方法。事實上,許多硬件設計師發現狀態分析儀中有許多極有價值的工具。

一個邏輯電路的“狀態”是數據有效時對總線或信號線的采樣樣本。例如,取一個簡單的“D”觸發器。“D”輸入端的數據直到時鐘正沿到來時才有效。這樣,觸發器的狀態就是正時鐘沿產生時的狀態。

現在,假定我們有8個這樣的觸發器并聯。所有8個觸發器都連到同樣的時鐘信號上。當時鐘線上產生正跳變時,所有8個觸發器都要捕獲各自“D”輸入的數據。這樣,每當時鐘線上正跳變時就產生一個狀態,這8條線類似于微處理器總線。如果我們把狀態分析儀接到這8條線上,并告訴它在時鐘線正跳變時收集數據,狀態分析儀將照此執行。除非時鐘跳到高電平,否則輸入的任何活動將不被狀態分析儀捕獲。

定時分析儀由內部時鐘控制采樣,因此它是對被測系統作異步采樣。而狀態分析儀從系統得到采樣時鐘,因此它是對系統同步采樣。狀態分析儀通常用列表方式顯示數據,而定時分析儀用波形圖顯示數據。

理解時鐘

在定時分析儀中,采樣是沿著單一內部時鐘的方向進行,從而使事情非常簡單。但微處理器系統中往往會有若干個“時鐘”。假定某個時刻我們要在RAM中的一個特定地址上觸發,并查看所保存的數據;再假定使用的微處理器是Zilog公司的 Z80。

為了用狀態分析儀從Z80捕獲地址,我們要在MREQ線為低時進行捕獲。而為了捕獲數據,需要在WR線為低(寫周期)或RD線為低(讀周期)時讓分析儀采樣。某些微處理器可在同一條線上對數據和地址進行多路轉換。分析儀必須能讓時鐘信息來自相同的信號線,而非來自不同的時鐘線。

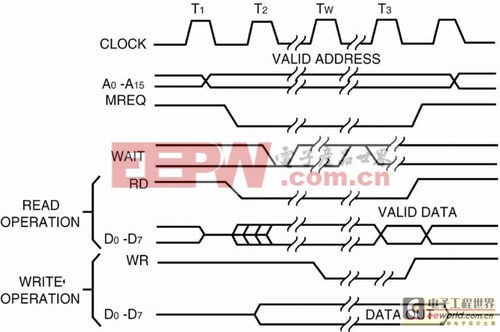

圖 4 RAM 定時波形圖

在讀寫周期期間,Z80首先把一個地址放在地址總線上。接著設定MREQ線在該地址對存儲器的讀或寫有效。最后根據現在是讀還是寫對RD或WR線斷言。WR線只有在總線數據有效后才被設定。這樣,定時分析儀就作為多路分配器在適當的時間捕獲地址,然后在同一信號線上捕獲產生的數據。

觸發狀態分析

像定時分析儀一樣,狀態分析儀也提供限定所要保存數據的功能。如果我們要尋找地址總線上由高低電平構成的特定碼型,可告訴分析儀在找到該模式時開始保存,直到分析儀的存儲器完全裝滿。

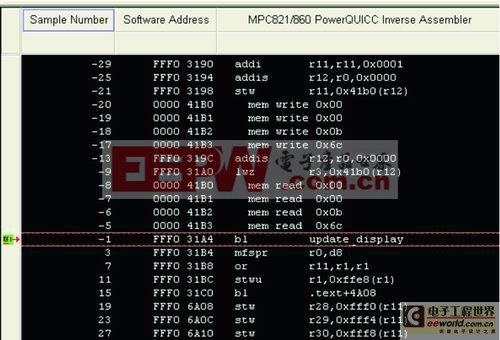

這些信息可以用十六進制或二進制格式顯示。但在解碼至匯編碼時,十六進制可能更為方便。在使用處理器時,應把這些特定的十六進制字符與處理器指令相比較。大多數分析儀制造商設計了稱為反匯編器的軟件包,這些軟件包把十六進制代碼翻譯成易于閱讀的匯編碼。

圖 5 把十六進制碼翻譯成匯編碼

序列級和選擇性保存

狀態分析儀具有幫助觸發和存儲的“序列級”數據。序列級使您能比單一觸發點更精確地限定要保存的數據。也就是說可使用更精確的數據窗,而不必存儲不需要的信息。

選擇性的保存意味著可只保存較大整體中的一部分。例如,假定我們有一個計算給定數平方的匯編例程。如果該例程不能正確計算平方,我們就告訴狀態分析儀捕獲這一例程。具體做法是先讓狀態分析儀尋找該例程的起點。當它找到起始地址時,我們再告訴它尋找終止地址,并保存兩者之間的所有信息。當發現例程結束時,我們告訴分析儀停止狀態保存。

探測解決方案

為進行調試,向數字系統施加的物理連接必須方便可靠,對被調試的目

評論