DAC/比較器架構與集成ADC優(yōu)勢比較

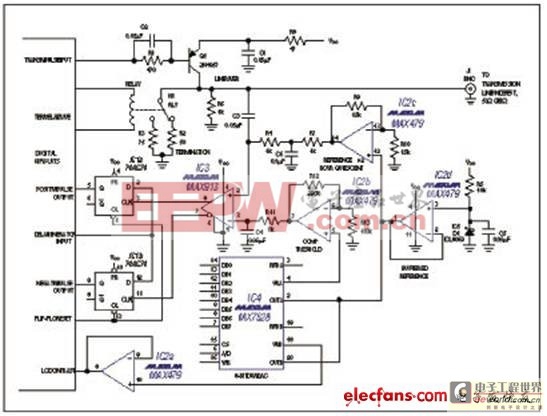

實際應用中的手持式TDR模擬前端(圖9)能夠說明上述觀點。為了便于說明,這里沒有包括數(shù)字電路。盡管簡單并且沒有特殊元件,該電路仍具有很好性能。能夠可靠地測量端接阻抗并且對于500英尺長的電纜具有5%測量精度。可測量長達2000英尺的開路或短路故障。重要的是,系統(tǒng)(包括顯示和數(shù)字電路)可在9V堿性電池下工作長達20小時。

圖9中比較器(IC3)采用單電源供電、地電位檢測以及僅10ns傳輸延遲。DAC(IC4)為雙通道器件,一方面用于脈沖高度測量,另一方面驅(qū)動LCD對比度控制(如圖3)。注意DAC為反向驅(qū)動;電流輸出端連接在一起由經(jīng)過緩沖的電壓基準驅(qū)動,基準輸入作為電壓輸出(每路帶有一個外部放大器緩沖)。

利用簡單的脈沖單穩(wěn)態(tài)電路(沒有列出)驅(qū)動Q1基極,利用正向、持續(xù)時間為10ns的脈沖依次驅(qū)動電纜。電纜的所有反射通過C3耦合到比較器。

IC5為1.2V輸出帶隙基準,由放大器IC2d緩沖,為IC4雙路DAC提供基準電壓。該基準電壓被IC2c兩倍增益放大器放大后,為比較器同相輸入提供2.5V直流電平。DAC A在比較器反相輸入端施加一個0至3.8V電壓。高于2.5V的電平用來判斷正向脈沖高度,低于2.5V的電平用來判斷負向脈沖幅度。

每個輸入到傳輸線的脈沖還經(jīng)過了數(shù)字電路可變延遲線,該延遲線是由計數(shù)器控制的20ns延遲單元串接而成。來自數(shù)字部分經(jīng)過延遲的脈沖驅(qū)動兩個觸發(fā)器(IC1a和IC1b)的D輸入端,觸發(fā)器由比較器互補TTL輸出輪流觸發(fā)。這樣,時間測量取決于返回脈沖和通過延遲線脈沖的競爭:如果D輸入比時鐘變化到來得早,觸發(fā)器輸出為高;否則,輸出為低。

測量時,將DAC輸出設置為最低值并重復調(diào)整延遲,直到觸發(fā)器輸出保持為零,讀取計數(shù)器。同樣,測量返回脈沖高度時,重復調(diào)整DAC輸出直到觸發(fā)器輸出保持為零,然后讀取DAC。注意,兩個觸發(fā)器需要捕獲正脈沖和負脈沖的前沿。前沿是指正脈沖的上升沿和負脈沖的下降沿;如果兩個脈沖施加到一個觸發(fā)器,脈沖寬度可能產(chǎn)生人們所不期望的延遲。

評論