模擬BIST的四項基本原則

模擬BIST的最后原則是,必須通過與上下測試極限值的比較,將其結果輸出為一個數字測量值以及合格/不合格的比特。如果要將一個模擬的電壓結果送至片外做特性描述,它就可能遭到損壞,并且可能需要混合信號ATE。一個未在片上與極限值比較過的數字結果可能需要用ATE去捕捉和分析數字字,而不是單個比特,這就不能使用最常見的測試模式語言WGL(波形生成語言)和STIL(標準測試界面語言),以及很多低成本的測試儀。單有合格/不合格的結果將無法確定參數特性,也缺乏測量的可重復性,而這是設定測試極限的一個基本步驟。

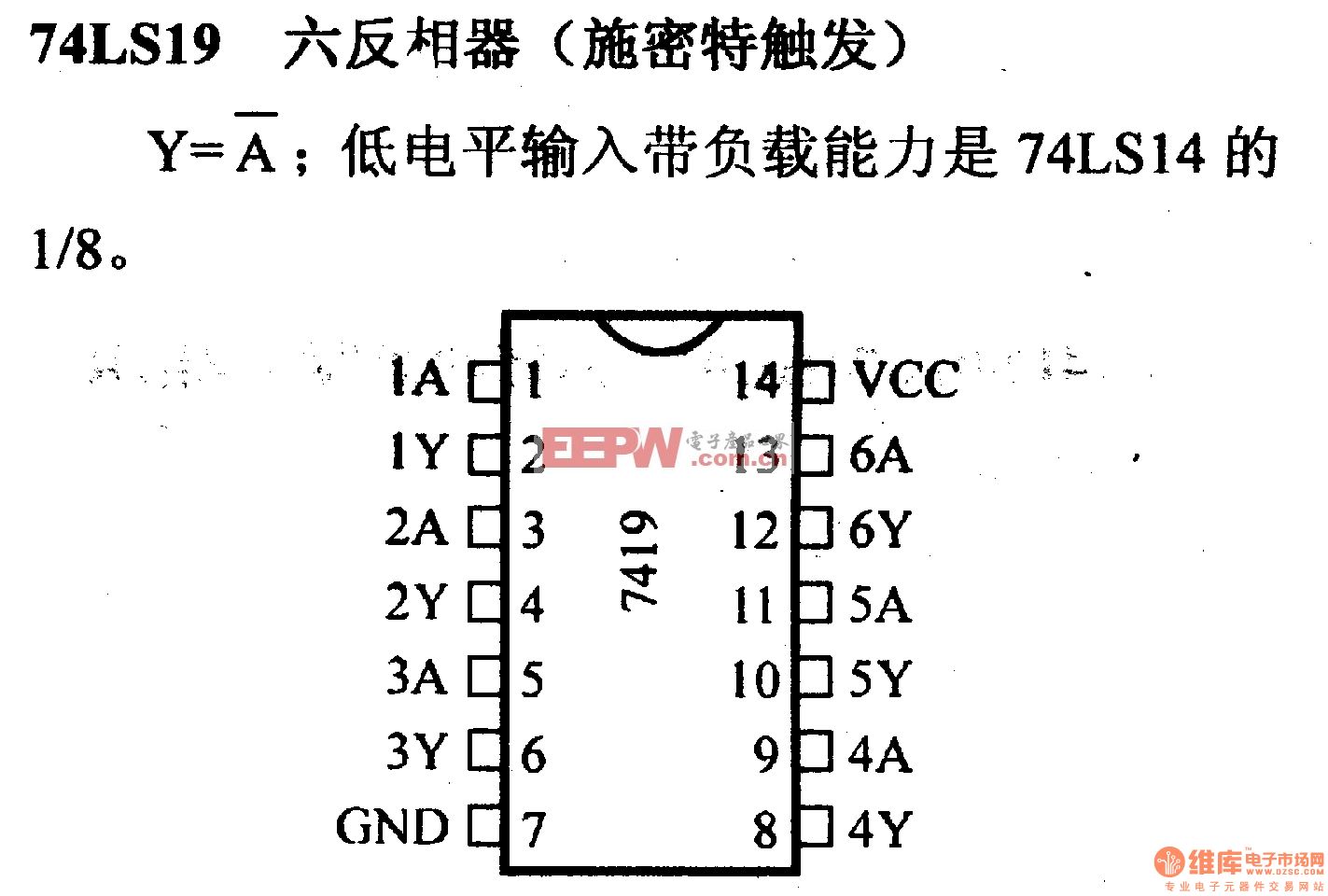

了解了這些基礎原則,就明白,實用PLL BIST既沒有采用模擬電路,也沒有使用延遲線,因此它對噪聲的敏感度弱于待測PLL。例如,PLL必須每納秒生成一個低抖動邊沿,并盡量減小抖動的累積。但是,PLL BIST可以用一個預測試的低抖動時鐘對邊沿作欠采樣,時鐘通過幾個數字反相器傳送,這些反相器有快速的轉換性能,盡量減少附加的抖動。

如果沒有預測試的時鐘,則PLL可以對相同芯片上工作在一個略為異步頻率的其它PLL邊沿作采樣。獲得的抖動測量結果是兩個抖動水平之和;隨機抖動不可能相互抵消。在一個直方圖中增加很多這類采樣,可以降低寄生噪聲的影響,并且以與任何干擾相同速率采樣,可以進一步降低這種影響。

4 模擬BIST的需求

過去15年來,很少有什么人提出的模擬BIST技術包含了上述所有原則。但所有這些原則都是BIST實用性與性價比的關鍵。開發一種實用的模擬BIST已被證明有太高的挑戰性,但工程師們無疑將開發出一些包含這 些原則的技術,因為對它們的需求在不斷增加。

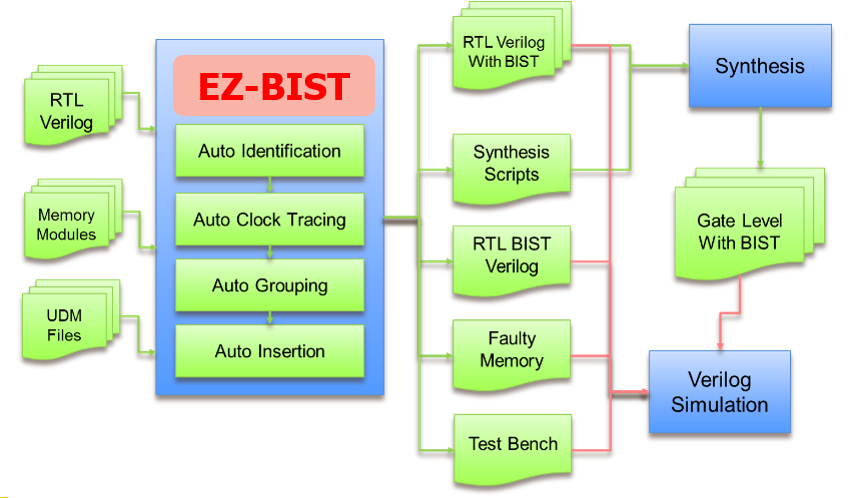

SoC中正在加入更多的系統模擬功能,有更多的管腳數和門數,所有這些都推升了測試時間與測試成本。增加嵌入閃存會大大增加測試時間(遠不止一分鐘),從而絕對需要多址的測試,這種要求又推動了對低管腳接入以及更多模擬測試資源的需求。

評論