基于FPGA/CPLD設(shè)計(jì)與實(shí)現(xiàn)UART

uart(即universal asynchronous receiver transmitter 通用異步收發(fā)器)是廣泛使用的串行數(shù)據(jù)傳輸協(xié)議。uart允許在串行鏈路上進(jìn)行全雙工的通信。

---串行外設(shè)用到rs232-c異步串行接口,一般采用專用的集成電路即uart實(shí)現(xiàn)。如8250、8251、ns16450等芯片都是常見的uart器件,這類芯片已經(jīng)相當(dāng)復(fù)雜,有的含有許多輔助的模塊(如fifo),有時(shí)我們不需要使用完整的uart的功能和這些輔助功能。或者設(shè)計(jì)上用到了fpga/cpld器件,那么我們就可以將所需要的uart功能集成到fpga內(nèi)部。使用vhdl將uart的核心功能集成,從而使整個(gè)設(shè)計(jì)更加緊湊、穩(wěn)定且可靠。本文應(yīng)用eda技術(shù),基于fpga/cpld器件設(shè)計(jì)與實(shí)現(xiàn)uart。

一 uart簡(jiǎn)介

1 uart結(jié)構(gòu)

uart主要有由數(shù)據(jù)總線接口、控制邏輯、波特率發(fā)生器、發(fā)送部分和接收部分等組成。

功能包括微處理器接口,發(fā)送緩沖器(tbr)、發(fā)送移位寄存器(tsr)、幀產(chǎn)生、奇偶校驗(yàn)、并轉(zhuǎn)串、數(shù)據(jù)接收緩沖器(rbr)、接收移位寄存器(rsr)、幀產(chǎn)生、奇偶校驗(yàn)、串轉(zhuǎn)并。

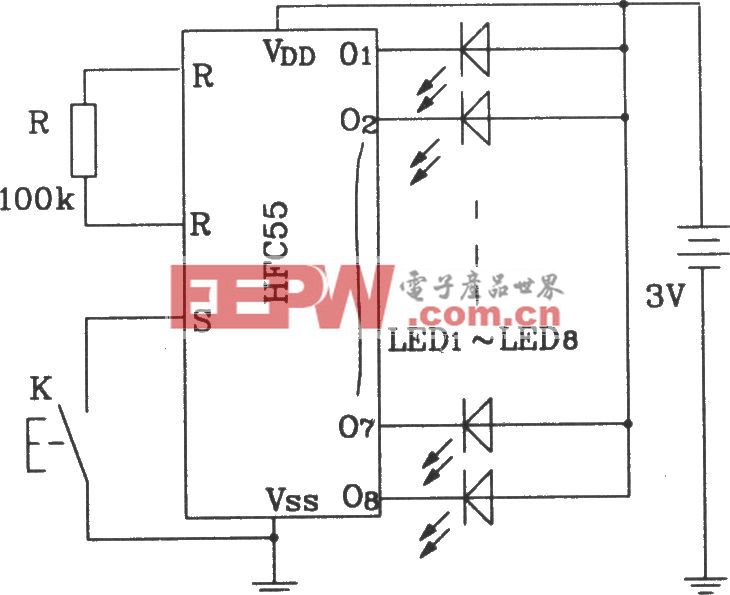

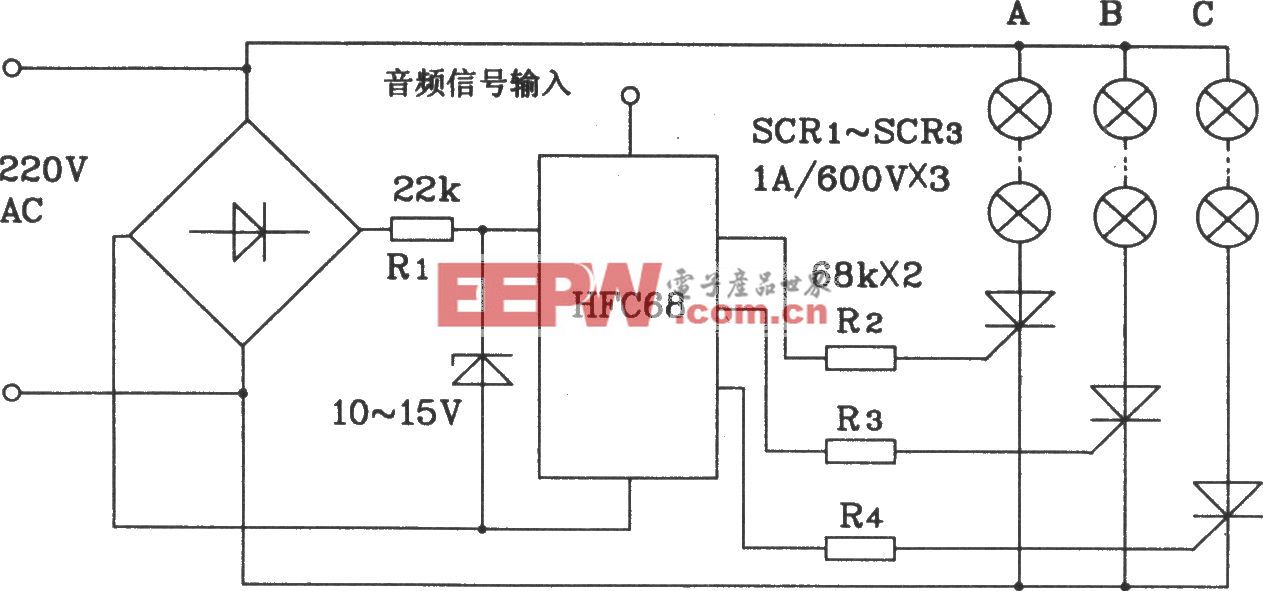

圖1是uart的典型應(yīng)用。

2 uart的幀格式

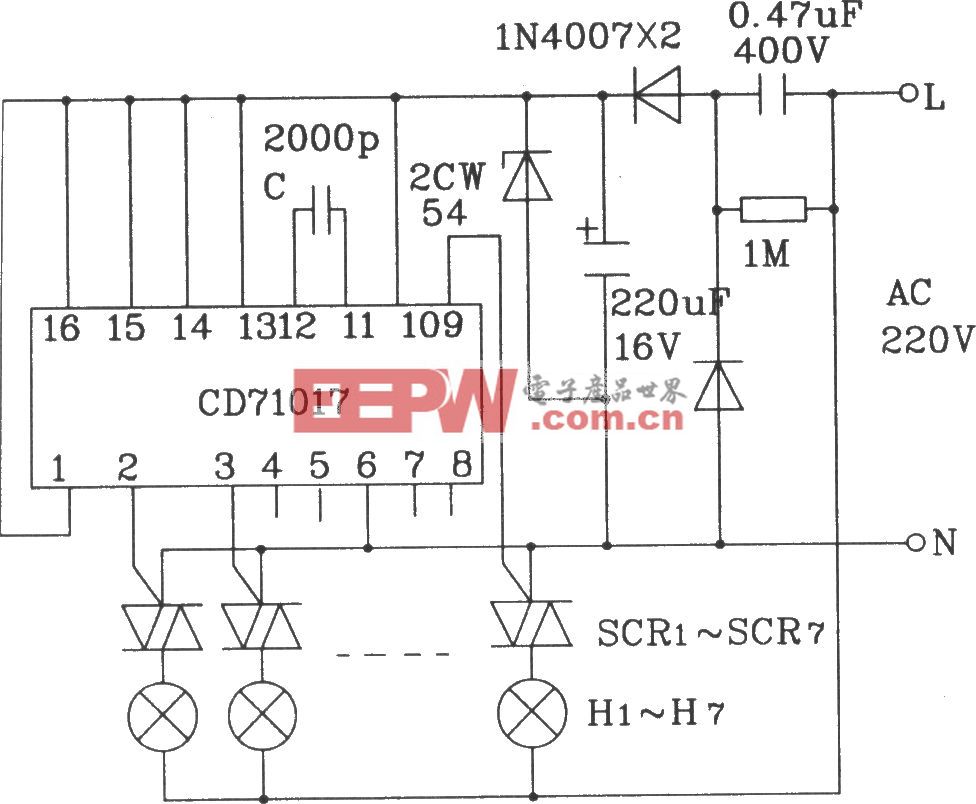

uart的幀格式如圖2所示。

包括線路空閑狀態(tài)(idle,高電平)、起始位(start bit,低電平)、5~8位數(shù)據(jù)位(data bits)、校驗(yàn)位(parity

bit,可選)和停止位(stop bit,位數(shù)可為1、1.5、2位)。

---這種格式是由起始位和停止位來(lái)實(shí)現(xiàn)字符的同步。

---uart內(nèi)部一般有配置寄存器,可以配置數(shù)據(jù)位數(shù)(5~8位)、是否有校驗(yàn)位和校驗(yàn)的類型、停止位的位數(shù)(1,1.5,2)等設(shè)置。

二 uart的設(shè)計(jì)與實(shí)現(xiàn)

1 uart發(fā)送器

發(fā)送器每隔16個(gè)clk16時(shí)鐘周期輸出1位,次序遵循1位起始位、8位數(shù)據(jù)位(假定數(shù)據(jù)位為8位)、1位校驗(yàn)位(可選)、1位停止位。

cpu何時(shí)可以往發(fā)送緩沖器tbr寫入數(shù)據(jù),也就是說(shuō)cpu要寫數(shù)據(jù)到tbr時(shí)必須判斷當(dāng)前是否可寫,如果不判這個(gè)條件,發(fā)送的數(shù)據(jù)會(huì)出錯(cuò)。

數(shù)據(jù)的發(fā)送是由微處理器控制,微處理器給出wen信號(hào),發(fā)送器根據(jù)此信號(hào)將并行數(shù)據(jù)din[7..0]鎖存進(jìn)發(fā)送緩沖器tbr[7..0],并通過(guò)發(fā)送移位寄存器tsr[7..0]發(fā)送串行數(shù)據(jù)至串行數(shù)據(jù)輸出端dout。在數(shù)據(jù)發(fā)送過(guò)程中用輸出信號(hào)tre作為標(biāo)志信號(hào),當(dāng)一幀數(shù)據(jù)發(fā)送完畢時(shí),tre信號(hào)為1,通知cpu在下個(gè)時(shí)鐘裝入新數(shù)據(jù)。

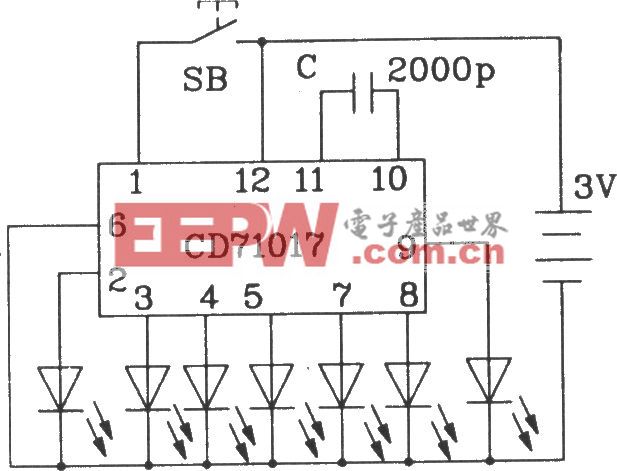

發(fā)送器端口信號(hào)如圖3所示。

引入發(fā)送字符長(zhǎng)度和發(fā)送次序計(jì)數(shù)器length_no,實(shí)現(xiàn)的部分vhdl程序如下。

if std_logic_vector(length_no) = “0001” then

tsr <= tbr ; --發(fā)送緩沖器tbr數(shù)據(jù)進(jìn)入發(fā)送移位寄存器tsr

tre <= 0 ; --發(fā)送移位寄存器空標(biāo)志置“0”

elsif std_logic_vector(length_no) = “0010” then

dout <= 0 ; --發(fā)送起始位信號(hào)“0”

elsif std_logic_vector(length_no) >= “0011” and std_logic_vector(length_no)

<= “1010” then

tsr <= 0 & tsr(7 downto 1); --從低位到高位進(jìn)行移位輸出至串行輸出端dout

dout <= tsr(0) ;

parity <= parity xor tsr(0) ; --奇偶校驗(yàn)

elsif std_logic_vector(length_no) = “1011” then

dout <= parity ; 校驗(yàn)位輸出

elsif std_logic_vector(length_no) = “1100” then

dout <= 1 ; --停止位輸出

tre <= 1 ; --發(fā)送完畢標(biāo)志置“1”

end if ;

發(fā)送器仿真波形如圖4所示。

2 uart接收器

串行數(shù)據(jù)幀和接收時(shí)鐘是異步的,發(fā)送來(lái)的數(shù)據(jù)由邏輯1變?yōu)檫壿?可以視為一個(gè)數(shù)據(jù)幀的開始。接收器先要捕捉起始位,確定rxd輸入由1到0,邏輯0要8個(gè)clk16時(shí)鐘周期,才是正常的起始位,然后在每隔16個(gè)clk16時(shí)鐘周期采樣接收數(shù)據(jù),移位輸入接收移位寄存器rsr,最后輸出數(shù)據(jù)dout。還要輸出一個(gè)數(shù)據(jù)接收標(biāo)志信號(hào)標(biāo)志數(shù)據(jù)接收完。

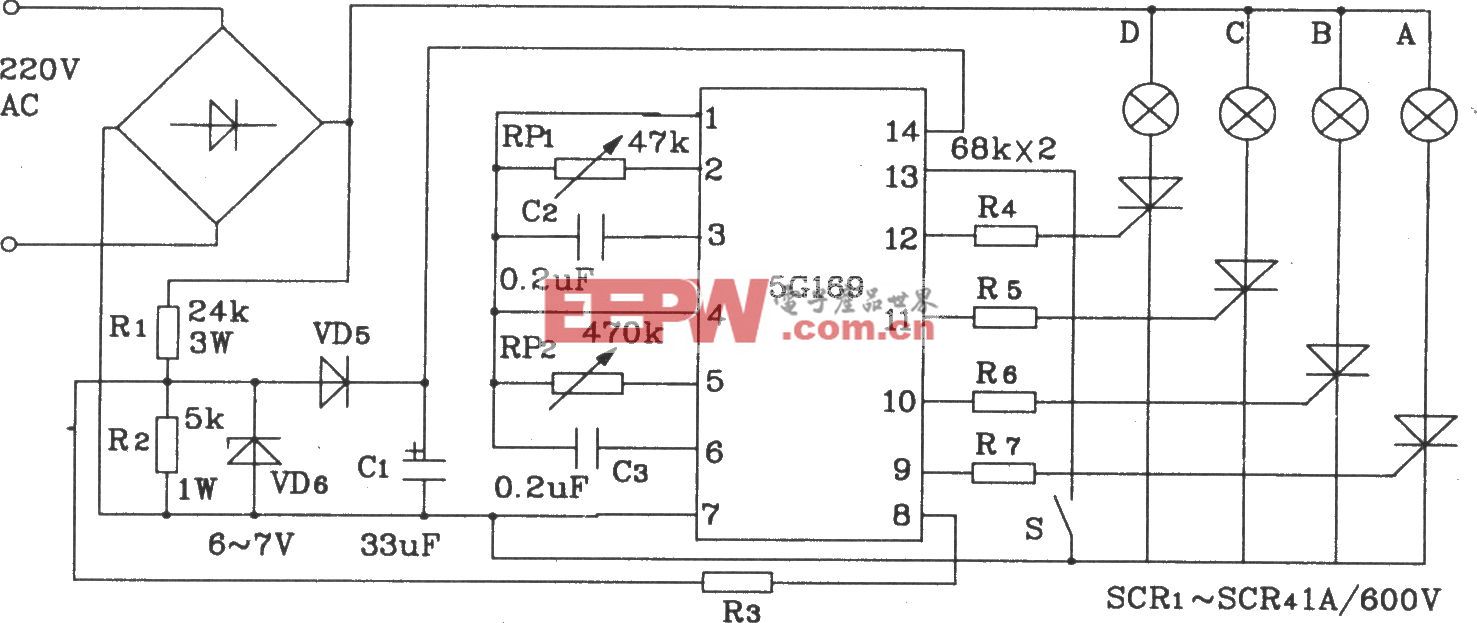

接收器的端口信號(hào)如圖5所示。

實(shí)現(xiàn)的部分vhdl程序如下。

elsif clk1xevent and clk1x = 1 then

if std_logic_vector(length_no) >= “0001” and std_logic_vector(length_no)

<= “1001” then

數(shù)據(jù)幀數(shù)據(jù)由接收串行數(shù)據(jù)端移位入接收移位寄存器

rsr(0) <= rxda ;

rsr(7 downto 1) <= rsr(6 downto 0) ;

parity <= parity xor rsr(7) ;

elsif std_logic_vector(length_no) = “1010” then

rbr <= rsr ; --接收移位寄存器數(shù)據(jù)進(jìn)入接收緩沖器

......

end if ;

接收器仿真波形如圖6所示。

3 波特率發(fā)生器

uart的接收和發(fā)送是按照相同的波特率進(jìn)行收發(fā)的。波特率發(fā)生器產(chǎn)生的時(shí)鐘頻率不是波特率時(shí)鐘頻率,而是波特率時(shí)鐘頻率的16倍,目的是為在接收時(shí)進(jìn)行精確地采樣,以提出異步的串行數(shù)據(jù)。

根據(jù)給定的晶振時(shí)鐘和要求的波特率算出波特率分頻數(shù)。

波特率發(fā)生器仿真波形如圖7所示。

三 小結(jié)

通過(guò)波特率發(fā)生器、發(fā)送器和接收器模塊的設(shè)計(jì)與仿真,能較容易地實(shí)現(xiàn)通用異步收發(fā)器總模塊,對(duì)于收發(fā)的數(shù)據(jù)幀和發(fā)生的波特率時(shí)鐘頻率能較靈活地改變,而且硬件實(shí)現(xiàn)不需要很多資源,尤其能較靈活地嵌入到fpga/cpld的開發(fā)中。在eda技術(shù)平臺(tái)上進(jìn)行設(shè)計(jì)、仿真與實(shí)現(xiàn)具有較好的優(yōu)越性。

評(píng)論