采用Verilog的數字跑表設計

數字跑表的顯示可以通過編寫數碼管顯示程序來實現,本實例只給出數字跑表的實現過程。讀者還可以通過增加小時的計時功能,實現完整的跑表功能。

實例目標

本實例主要實現了計數及進位的設計,通過幾個always模塊的設計實現一個特定用途的模塊——數字跑表。通過本實例,讀者應達到下面的一些實例目標。

? 初步掌握Verilog語言的設計方法。

? 完成一個數字跑表的設計。

原理簡介

本數字跑表首先要從最低位的百分秒計數器開始,按照系統時鐘進行計數。計數至100后向秒計數器進位,秒計數器以百分秒計數器的進位位為時鐘進行計數。計數至60后向分計數器進位,分計數器以秒計數器的進位位為時鐘進行計數,讀者可以自行增加小時計數器。

數字跑表巧妙地運用進位位作為計數時鐘來減少計數的位數。如果統一使用系統時鐘作為計數時鐘,那秒計數器將是一個6000進制的計數器,而分計數器將是一個3600000進制的計數器。這樣將極大的浪費FPGA的邏輯資源。而使用進位位作為計數時鐘,只需要一個100進制的計數器和兩個60進制的計數器。

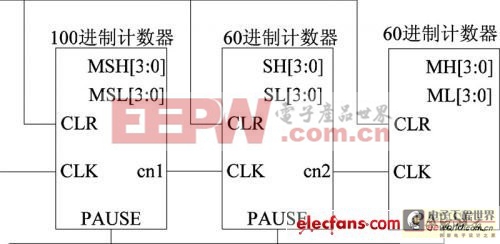

如圖是本實例的數字跑表模塊圖。

在實際的設計中,為了使計數器更加簡單,計數器使用高低位兩個計數器實現。100進制計數器分別是高位10進制計數器,低位10進制計數器;60進制計數分別是高位6進制計數器,低位10進制計數器。這樣整個數字跑表使用6個計數器實現。

同時由于10進制計數器重復使用了5次,可以使用獨立的模塊實現10進制計數器,這樣就可以通過模塊復用來節省整個模塊使用的資源。

數字跑表提供了清零位CLR和暫停位PAUSE,百分秒的時鐘信號可以通過系統時鐘分頻提供。分頻至1/100s,即可實現真實的時間計數。詳細的時鐘分頻設計讀者可參考相關的資料實現,在本實例中不再提供。

評論