平衡電子設(shè)備靜電防護和信號完整性設(shè)計

大多數(shù)的二極管廠商提供電流與電壓的關(guān)系曲線圖。雖然這些曲線圖通常使用8/20 μs脈沖而非IEC 61000-4-2 準(zhǔn)規(guī)定的脈沖,但是他們可用作電路阻抗的一般指標(biāo)。對于8/20μs脈沖,電流和電壓關(guān)系曲線完全是線性的,而且直線的斜率就是動態(tài)電阻值(Rdyn)。典型的ESD二極管動態(tài)電阻值(Rdyn)的變化范圍從低于一個歐姆到三個歐姆。聚合體也有非常低的電阻。

另一方面,用于高速輸入/輸出端口的低電容抑制器具有很高的動態(tài)電阻,其變化范圍是20歐姆或者更高值,這導(dǎo)致了被保護的ASIC電流值相對較高。事實上抑制器和變阻器從“被保護”的ASIC分流了很少的電流。因此上大部份的電流實際上傳到了ASIC。顯然,這一個特性使得他們很少被選用作ESD防護。

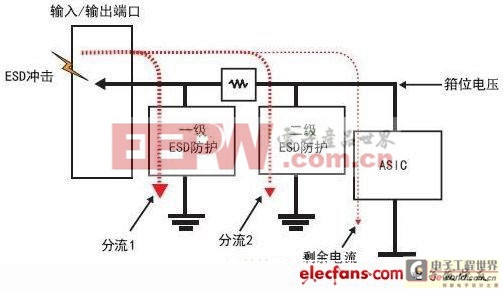

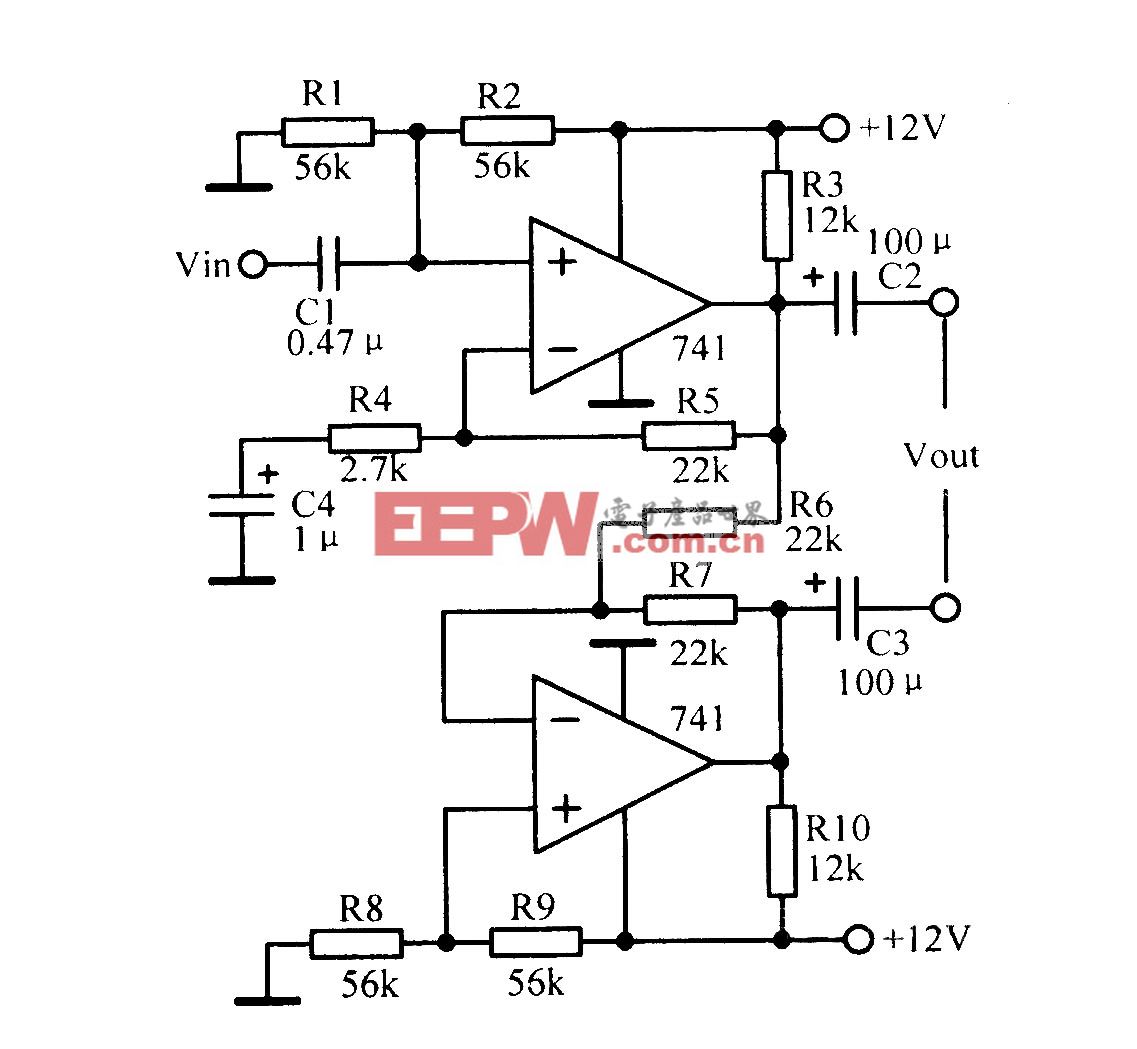

確保ESD防護的可靠性在傳統(tǒng)的ESD防護技術(shù)中,雖然半導(dǎo)體二極管提供了最好的ESD保護,但它們不能夠保護當(dāng)前采用的亞微米幾何尺寸制造的最新ASICs。通過采用傳統(tǒng)手段進一步的減少這些裝置的箝位電壓和動態(tài)電阻則意味著增加電容量-這在高速應(yīng)用中是個無法接受的取舍。一種新的ESD防護基本方法是利用新型雙箝位結(jié)構(gòu),這種結(jié)構(gòu)與電感、電阻一起集成了兩級低電容二極管連同電感和一個電阻器,通過這種方式能在保持信號完整性的同時,顯著地減少剩余電流、箝位電壓并提供有效地ESD保護,如下圖:

ESD防護電路圖

當(dāng)ESD沖擊發(fā)生時,電路結(jié)構(gòu)中的第一級開始抑制,分流大部份的電流并減小電壓。剩余電流經(jīng)過一個電阻后,沖擊第二級電路,這將進一步減小電壓,最終使流到ASIC的電流最小。

這種電路結(jié)構(gòu)能為高速USB,高清多媒體和個人計算機設(shè)計提供ESD保護。通過片上匹配、減小偏差和EMI并改進由于集總電感引起的TDR(時域反射計效應(yīng)),信號完整性得到改進。

評論