三電平輸入簡易檢測方法

現(xiàn)在有很多電路(例如IDT的可編程時(shí)鐘發(fā)生器)為了減少配置輸入引腳數(shù)目(亦可縮小電路封裝尺寸),輸入引腳除了常規(guī)的高(“1”)、低(“0”)2種電平狀態(tài)外,還增加了第三種狀態(tài):懸空(“Z”),IDT稱作“M”電平。這樣,2個(gè)輸入引腳就可給出9種配置:00、01、10、11、0M、1M、M0、M1、MM,比常規(guī)兩電平的4種配置多出6種。

實(shí)際應(yīng)用中,如果用戶希望在自己設(shè)計(jì)的電路(如:FPGA、MCU等)增加三電平輸入,檢測方法有三種:

1、對(duì)于FPGA,方法很簡單,使用下述VHDL語句即可:

if (input=’0’) rhen

//低電平

elsif (input=’1’)then

//高電平

else

//懸空

也可使用case語句直接判斷:”00”、”01”、”0Z” 、“1Z”等。

2、采用類似FPGA或DSP的弱上拉加下拉電阻(如100K)方法,當(dāng)輸入接GND、VCC或懸空時(shí),輸入內(nèi)部的電壓則為0V、VCC、1/2VCC,可以采用雙門檻比較器或AD轉(zhuǎn)換器判出1/2VCC狀態(tài)。

3、上述第2種方法判斷1/2VCC電平狀態(tài)比較麻煩,可采用下述更簡便的判斷方法:

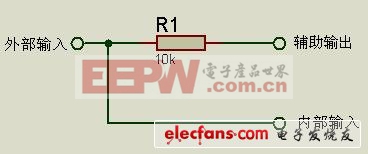

如上圖所示,電路內(nèi)部增加一個(gè)串聯(lián)10K電阻到外部輸入端的“輔助輸出”,當(dāng)“輔助輸出”輸出高低變化電平時(shí),“內(nèi)部輸入”檢測到這種變化,則“外部輸入”是懸空的,如不變,則“外部輸入”是固定高、低電平。

值得注意一點(diǎn)的是,對(duì)于三電平輸入引腳,一般外部不能再加上拉或下拉電阻,而是直接接VCC、 GND或懸空。

評(píng)論