∑-△ADC的降采樣濾波器方案

4.1.4 時鐘的處理

系統用到了多個分頻時鐘,為了方便后面布局布線做時鐘樹,本設計采用計數器產生使能信號進行分頻。

4.1.5 Design Compiler綜合

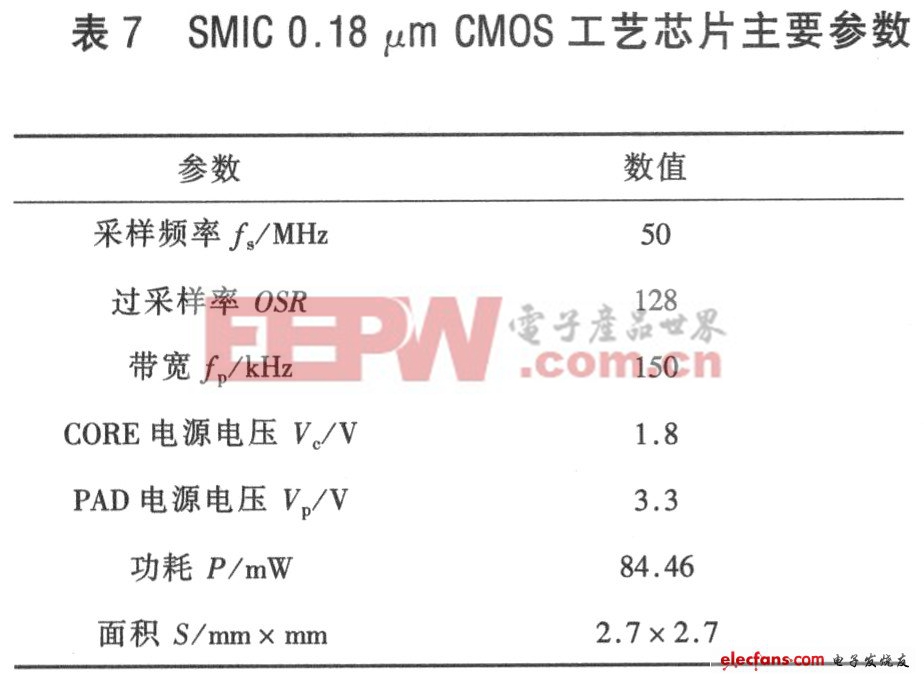

本設計采用SMIC 0.18μm CMOS工藝庫,將編寫的Verilog代碼用Synopsy的Design Compiler綜合,通過加上適當的約束條件反復優化,最終得到綜合結果。綜合結果通過Synopsys VCS仿真驗證。

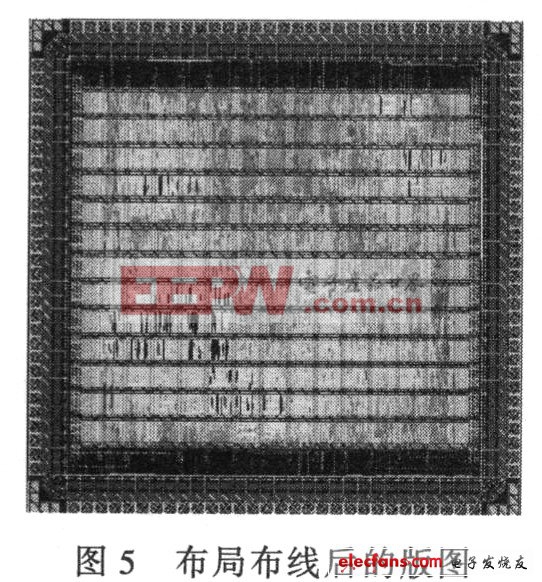

4.2 版圖設計

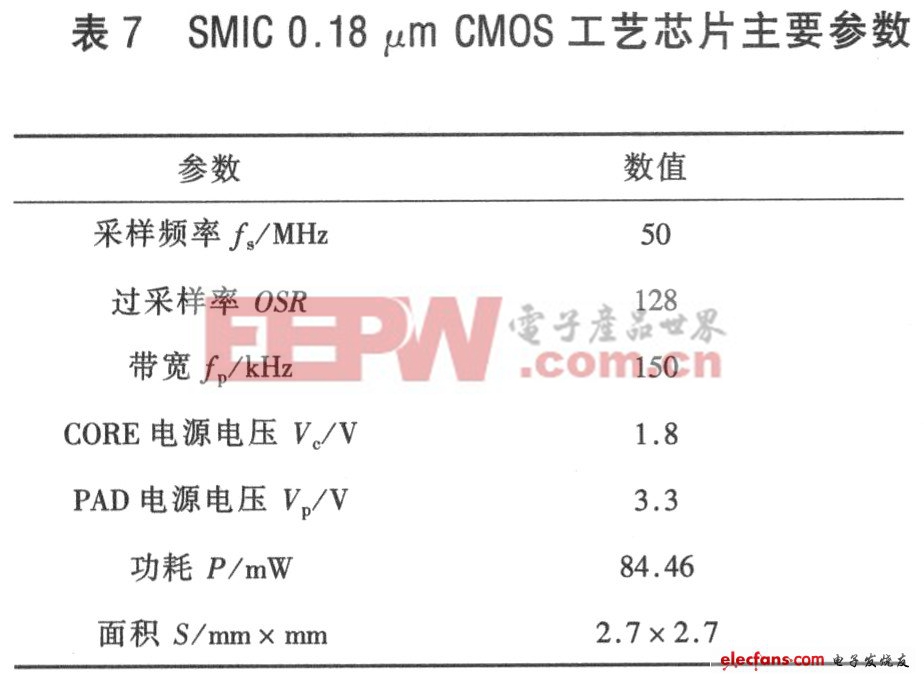

本設計采用Cadence Encounter對綜合后的濾波器的門級網表進行布局布線,圖5是完成布局布線后的版圖。芯片主要參數如表7所示。

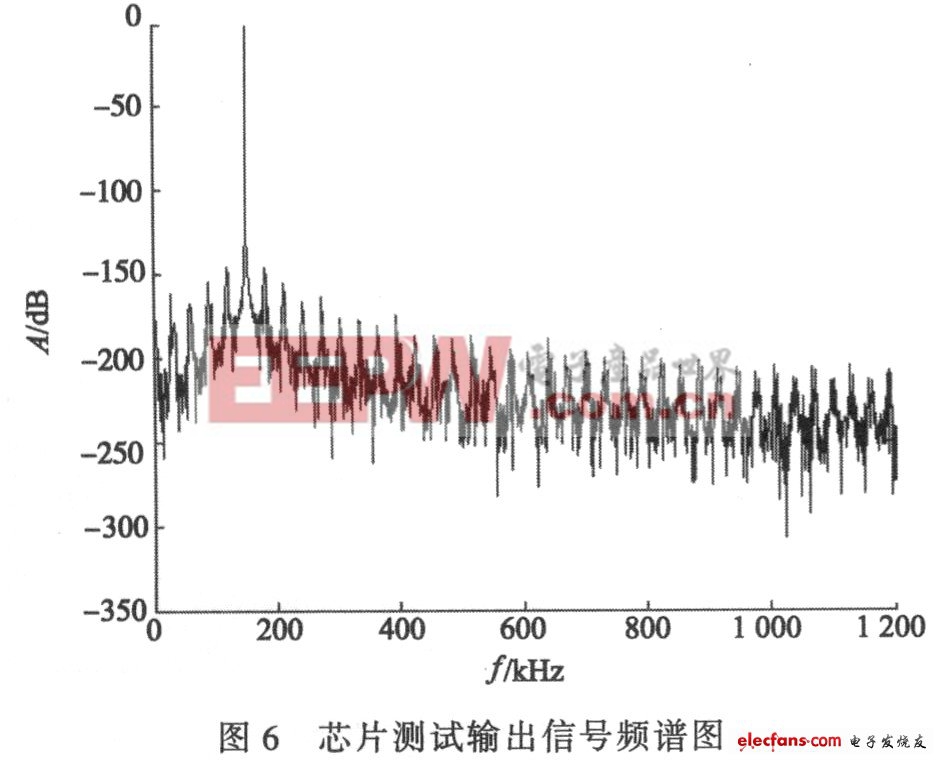

5 芯片測試

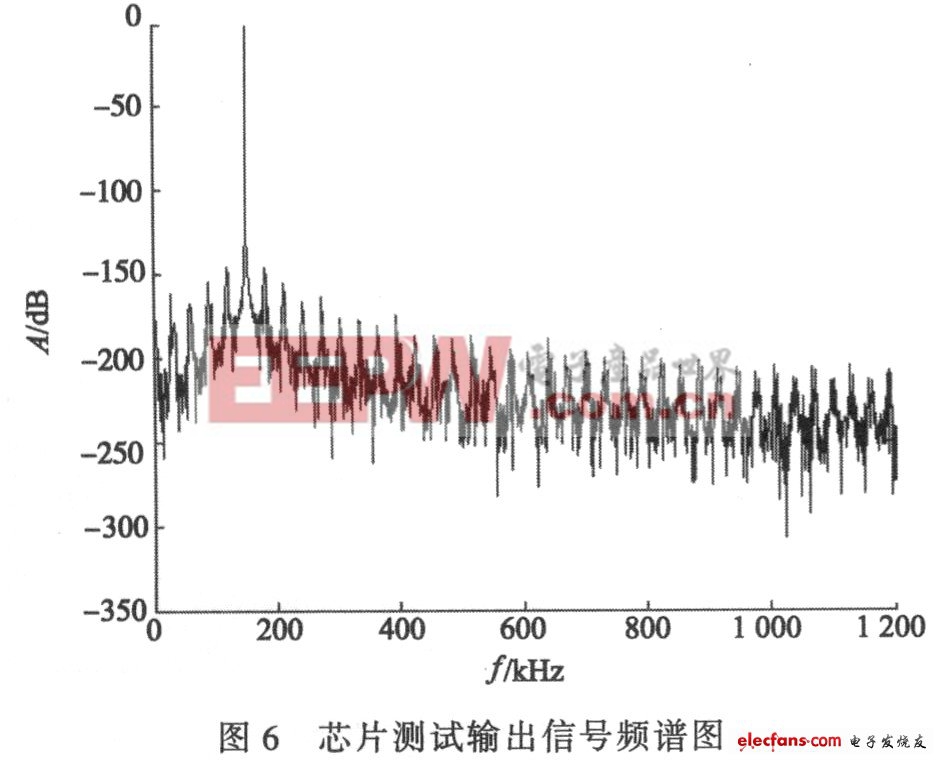

在模擬三階CRFB結構的∑-△調制器輸入的情況下,通過邏輯分析儀采集輸入為150 kHz正弦信號的輸出數據,并由計算得到的頻譜如圖6所示,信號與噪聲加失真比(SINAD)大于86 dB,滿足性能指標要求。

6 結論

通過Synopsy的Design Compiler進行電路綜合和Cadence Encounter進行布局布線,采用SMIC 0.18μm CMOS工藝實現。系統仿真和芯片測試結果表明,性能滿足設計指標要求。

電源濾波器相關文章:電源濾波器原理

評論