∑-ΔADC(第二部分):調節器

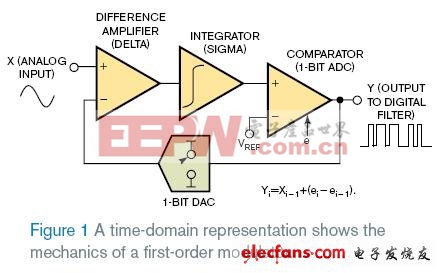

調節器測量模擬輸入信號和反饋DAC的模擬輸出。隨后一個積分器測量求和節點的模擬電壓輸出,為1位ADC呈現出一個斜坡信號。1位ADC轉換積分器輸出信號為數字一或零。使用系統時鐘,ADC將1位數字信號送到調節器輸出,也通過反饋回輸入,在這里1位DAC為等待。

1位ADC將信號量化為離散的輸出編碼,帶有轉換器的量化噪聲(ei)。調節器輸出等于輸入信號加上量化噪聲(ei–ei–1)。如這個公式所示,量化噪聲為調節器當前誤差(ei)減去前一個誤差(ei–1)的微分。時域輸出信號為以采樣頻率FS的輸入信號脈沖波形。如果將輸出脈沖序列平均,它等于輸入的信號值。

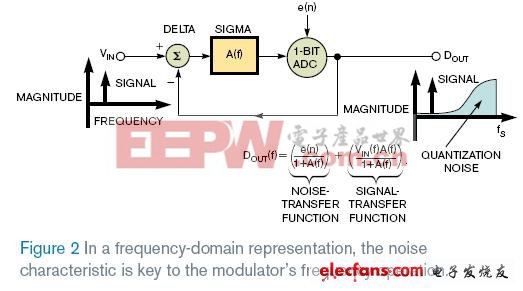

頻域圖反映了不同的問題(圖2)。時域輸出脈沖在頻域內表現為輸入信號(或毛刺)和變形的噪聲。圖2的噪聲特性是調節器頻率作用的關鍵。

不像大多數量化器,Σ-Δ調節器包括形成量化噪聲的積分器。調節器輸出的噪聲頻譜并不平滑。更重要的,在頻率分析中,可以看到積分器怎樣在更高頻率處形成噪聲,便于產生更高分辨率的結果。

圖2中調節器輸出顯示了調節器的量化噪聲在0Hz時開始為低電平,快速上升,然后在調節器采樣頻率為最大值處穩定。

二階調節器進行兩次積分,而不是僅有一次,是最小化低頻率量化噪聲的一種好方法。大多數Σ-Δ調節器具有更高的階數。例如,更常用的Σ-Δ轉換器的設計包括二、三、四、五或六階調節器。多階調節器在更高頻率形成更大的量化噪聲。

評論