ADC輸入噪聲利弊分析(二)

對于高速ADC,若要最大程度地提高SFDR,存在兩個基本限制:第一是前端放大器和采樣保持電路產生的失真;第二是ADC編碼器部分的實際傳遞函數的非線性所導致的失真。

提高SFDR的關鍵是盡可能降低以上兩種非線性。

要顯著降低ADC前端引起的固有失真,在ADC外部著力是徒勞的。然而,ADC編碼器傳遞函數的微分非線性可以通過適當利用擾動(即外部噪聲,與ADC的模擬輸入信號相加)來降低。

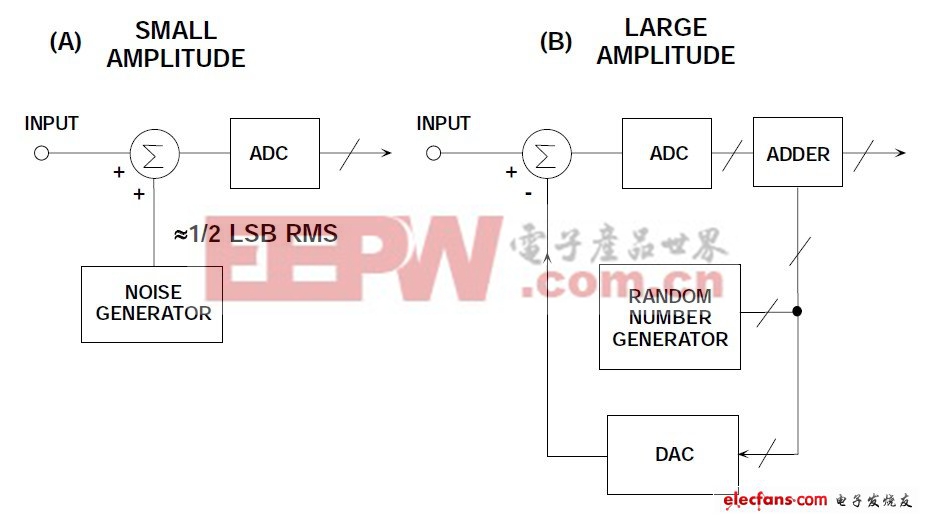

在一定的條件下,擾動可以改善ADC的SFDR(參考文獻2-5)。例如,即使在理想ADC中,量化噪聲與輸入信號也有某種相關性,這會降低ADC的SFDR,特別是當輸入信號恰好為采樣頻率的約數時。將寬帶噪聲(幅度約為? LSB rms)與輸入信號相加往往會使量化噪聲隨機化,從而降低其影響(見圖5A)。然而,在大多數系統中,信號之上有足夠的噪聲,因此無需額外添加擾動噪聲。ADC的折合到輸入端噪聲也可能足以產生同樣的效果。將寬帶均方根噪聲電平提高約1 LSB以上會成比例地降低ADC SNR,且性能不會有進一步的提高。

還有其它一些方案,都使用更大數量的擾動噪聲,使ADC的傳遞函數隨機化。圖5B還顯示了一個由驅動DAC的偽隨機數發生器組成的擾動噪聲源,此信號從ADC輸入信號中減去后,以數字方式增加到ADC輸出中,從而不會導致SNR性能顯著下降。這種技術本身有一個缺點,即隨著擾動信號的幅度增大,允許的輸入信號擺幅會減小。之所以需要減小信號幅度,是為了防止過驅ADC.應當注意,這種方案不能顯著改善ADC前端產生的失真,只能改善ADC編碼器傳遞函數的非線性所引起的失真。

圖5:利用擾動使ADC傳遞函數隨機化

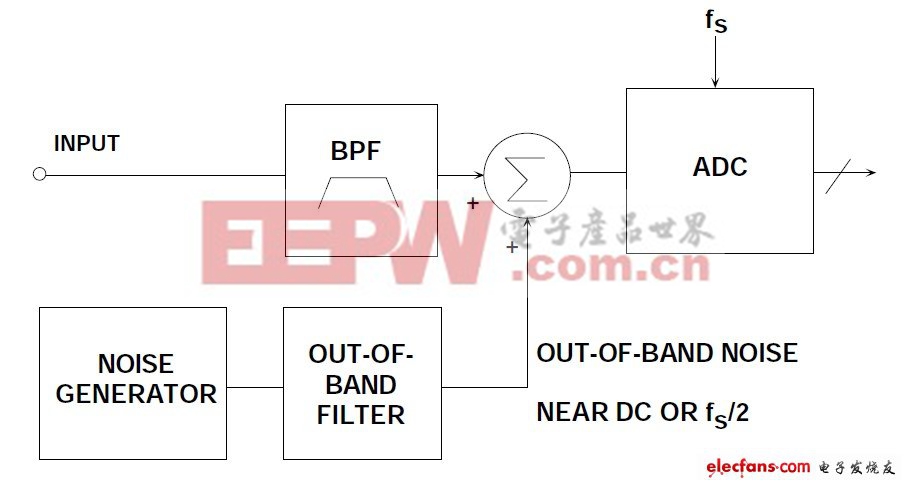

還有一種方法更容易實現,尤其是在寬帶接收機中,即注入信號目標頻帶以外的一個窄帶擾動信號,如圖6所示。一般來說,信號成分不會位于接近DC的頻率范圍,因此該低頻區常用于這種擾動信號。擾動信號可能還位于略低于fs/2的地方。相對于信號帶寬,擾動信號僅占用很小的帶寬(數百kHz帶寬通常即足夠),因此SNR性能不會像在寬帶擾動下那樣顯著下降。

圖6:注入帶外擾動以改善ADC SFDR

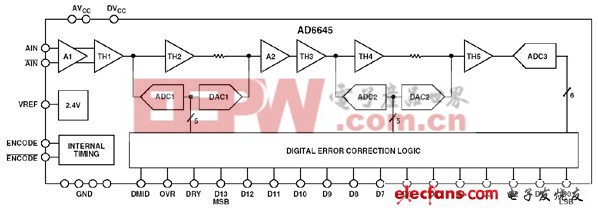

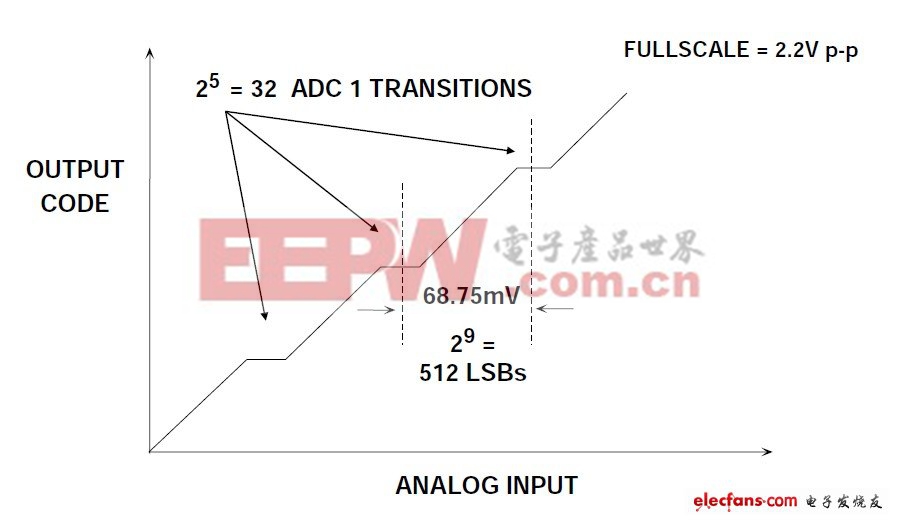

分級流水線式ADC,例如圖7所示的14位105 MSPS ADC AD6645,在ADC范圍內的特定代碼躍遷點有非常小的差分非線性誤差。AD6645由一個5位ADC1、一個5位ADC2和一個6位ADC3組成。嚴重的DNL誤差僅出現在ADC1躍遷點,第二級和第三級ADC的DNL誤差非常小。ADC1有25 = 32個相關的決策點,每隔68.75 mV (29 = 512 LSB)出現一個(2.2 V滿量程輸入范圍)。圖8以夸張形式顯示了這些非線性誤差。

圖7:14位105 MSPS ADC AD6645簡化框圖

圖8:AD6645分級點DNL誤差(夸張顯示)

對于最高約為200 MHz的模擬輸入,AD6645前端產生的失真成分與編碼器產生的失真相比可忽略不計。這就是說,AD6645傳遞函數的靜態非線性是SFDR性能的主要限制。

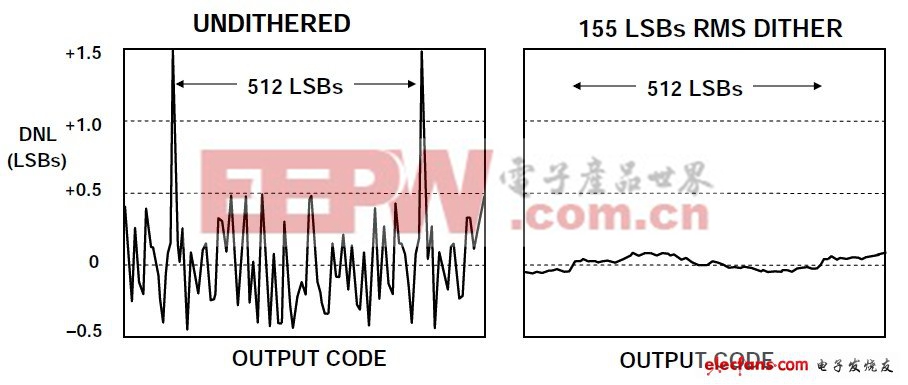

目標是選擇適當的帶外擾動量,使得這些微小DNL誤差的影響在ADC整個輸入范圍內隨機化,從而降低平均DNL誤差。這可以通過實驗方法確定,覆蓋大約兩個ADC1躍遷區的峰峰值擾動噪聲對DNL的改善最佳。更高的噪聲量不會明顯改善DNL.兩個ADC1躍遷區覆蓋1024 LSB峰峰值,或者大約155 LSB rms(峰峰值高斯噪聲除以6.6即得到均方根值)。

圖9中的第一幅圖顯示一小部分輸入信號范圍內的無擾動DNL.水平軸經過放大,以顯示兩個相距68.75 mV (512 LSB)的分級點。第二幅圖顯示增加155 LSB rms擾動后的DNL,該擾動量相當于大約–20.6 dBm.請注意,DNL得到顯著改善。

圖9:無擾動和有擾動的AD6645 DNL

擾動噪聲可以通過多種方式產生。可以使用噪聲二極管,但簡單地放大器寬帶雙極性運放的輸入電壓噪聲是更經濟的解決方案,這種方法已在參考文獻3、4、5中詳細說明,在此恕不贅述。

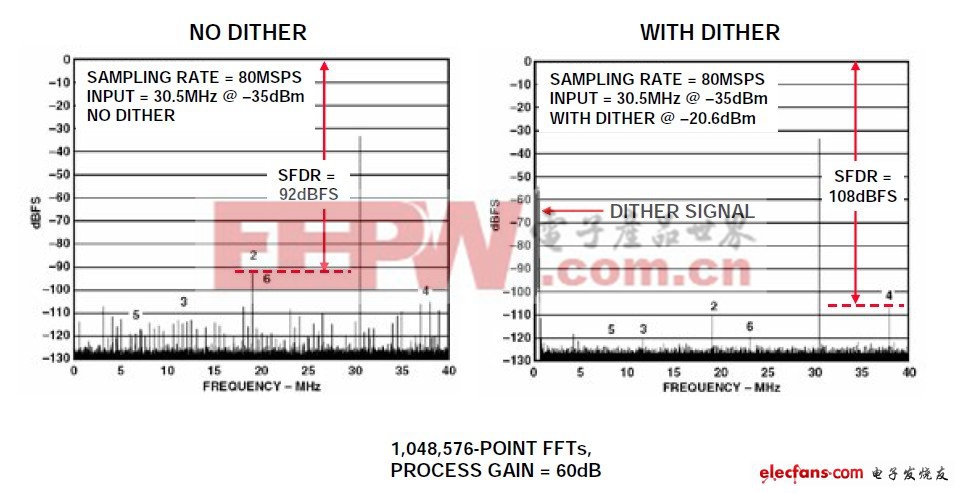

利用帶外擾動獲得的SFDR大幅改善結果如圖10的深(1,048,576點)FFT所示,其中AD6645以80 MSPS的速率對一個–35 dBm、30.5 MHz信號進行采樣。請注意,無擾動時SFDR約為92 dBFS,有擾動時約為108 dBFS,提高幅度達16 dB!

圖10:無擾動和有擾動的AD6645 FFT圖

AD6645 ADC由ADI公司于2000年推出,直到最近,它仍是代表SFDR極致性能的產品。自從推出該器件后,工藝技術和電路設計兩方面的進步推動ADC向更高性能發展,例如AD9444(14位、80 MSPS)、AD9445(14位、105/125 MSPS)和AD9446(16位、80/100 MSPS),這些ADC具有非常高的SFDR(對于70 MHz滿量程輸入信號,典型值大于90 dBc)和低DNL.

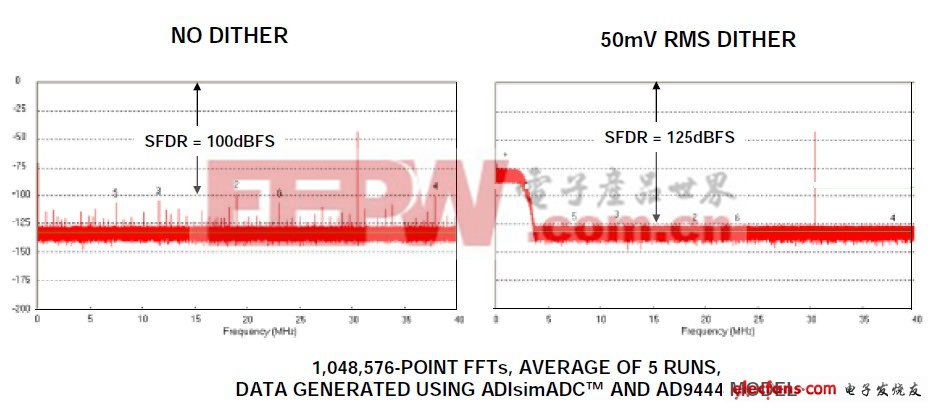

在一定的輸入信號條件下,增加適當的帶外擾動信號同樣可以改善SFDR性能。

圖11顯示了有擾動和無擾動下的AD9444(14位、80MSPS)FFT.在這些輸入條件下,添加擾動使SFDR提高25 dB.所示數據是利用ADIsimADC程序和AD9444模型獲得。

圖11:14位、80MSPS ADC AD9444,fs = 80MSPS,fin = 30.5MHz,信號幅度 = –40dBFS

雖然圖10和圖11所示的結果相當驚人,但不應認為,增加帶外噪聲擾動一定就會改善ADC的SFDR,或者在所有條件下都適用。正如之前提到的,擾動無法改善ADC前端電路的線性度。即使是近乎理想的前端,擾動的效果也將高度依賴于輸入信號的幅度和擾動信號本身的幅度。例如,當信號接近ADC的滿量程輸入范圍時,傳遞函數的積分非線性可能會成為確定SFDR的限制因素,擾動將沒有助益。務必認真研究數據手冊,某些情況下,其中可能給出了有擾動和無擾動的數據以及幅度和帶寬建議。擾動可能是更新一代中頻采樣ADC的內置特性。

結束語

在本文中,我們說明了所有ADC都有一定量的折合到輸入端噪聲。在精密、低頻測量應用中,以數字方式對ADC輸出數據求平均值可以降低該噪聲,代價是采樣速率會降低并且需要額外的硬件。該均值方法實際上可以提高ADC的分辨率,但無法降低積分非線性誤差。

評論