基于DSP的陣列聲波信號采集與處理系統的設計

引言

隨著傳感器由過去的單個變為陣列結構,儀器要處理的信號也由過去單一的參數信號變為復雜的圖像信號,同時,對信號的采集與處理也變得越來越復雜,研制一種陣列聲波信號采集與處理系統,并進而開發出一種陣列聲波測井儀,成為目前我國石油測井儀器發展的迫切需要。為此本文設計了一套基于DSP的陣列聲波信號采集與處理系統,此系統將作為正在研制的陣列聲波測井儀中的一部分,應用于油田勘探中。

系統總體方案設計

陣列聲波測井儀由聲系、電子線路和鋼外殼組成。聲系在最下端,由發出聲波的發射晶體和接收聲波并把其轉換成電信號的傳感器陣列組成。電子線路分為供電模塊、主CPU模塊和采集模塊。其中,主CPU模塊是陣列聲波測井儀的控制部分,它一方面把地面部分傳給采集模塊和聲系的參數傳給采集模塊和聲系,另一方面把采集模塊傳上來的數據傳給地面部分。采集模塊即為陣列聲波采集與處理系統,它的一端接聲系的傳感器陣列,另一端接主CPU,主要功能為在主CPU的控制下把前端傳感器陣列傳過來的信號采樣、數字化并進行一系列的處理,然后把處理結果上傳給主CPU。

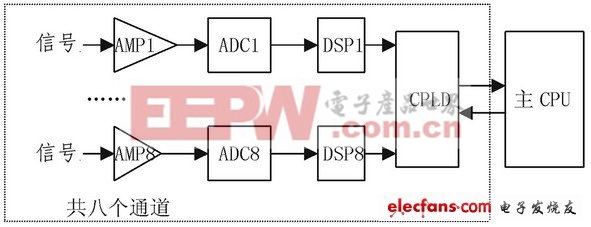

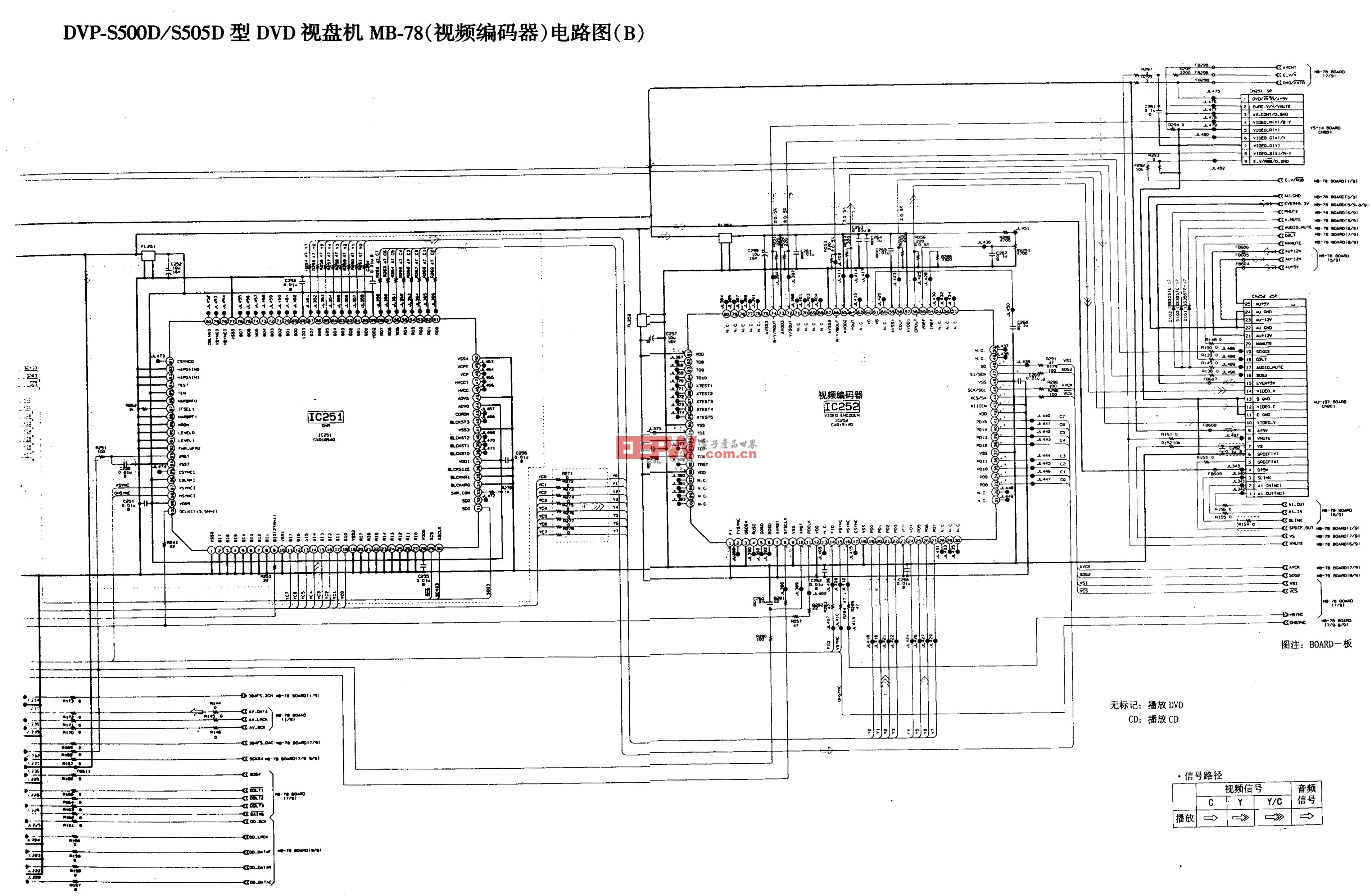

根據陣列聲波采集與處理系統的性能要求和可靠性與低功耗設計原則,本設計決定采用以DSP芯片為核心的八通道實現方案,如圖1所示。由于前端傳感器陣列送來的數據信號比較微弱,要先由放大器對信號進行放大,同時此放大器也可以有效地減弱或消除后端ADC對前端模擬聲波輸入信號的影響。放大器之后是ADC,從放大器到DSP形成一個采集與處理的通道,系統中這樣的通道共八個。而圖1中的CPLD是系統的控制邏輯部分。此外,考慮到系統可靠性和實時性的要求,本系統設計成每個通道都有一個DSP處理器而不是八個通道共用一個DSP處理器。

圖1 陣列聲波信號采集與處理系統總體結構示意圖

DSP設計

DSP芯片

由于整個陣列聲波測井儀的其它芯片均為+5V供電,陣列聲波采集與處理系統作為測井儀中的一部分,如果所選DSP芯片不是+5V供電,則需用電源轉換芯片進行電壓轉換,這不僅使電路變得復雜,而且也不利于系統性能提高。所以本設計選用了TI公司的DSP芯片—TMS320C542(以下簡稱C542)。

C542除具有TMS320C54x的一般優點外,其單周期定點指令執行時間為25ns,運行速度相對較高,能夠完成本系統采集與處理功能;且帶有一個 BSP自動緩沖串口和一個TDM時分復用串口,兩者都可用作SP標準同步串口。此外,無論是內核還是I/O引腳工作電壓均為+5V,所以使用時不需電壓轉換芯片。

自舉加載設計

傳統DSP系統程序代碼的引導裝載多以并行EPROM作為應用程序的存儲器方式,其最大弊端在于EPROM不支持在線擦寫,這會對系統的調試帶來很大的不便,特別是對于表貼封裝的存儲器,此方法基本不可用。

在本系統的設計中,采用了可以在線擦寫的FLASH代替EPROM作為程序代碼的存儲器。因而從根本上克服了傳統方法在系統調試上帶來的諸多不便,對表貼封裝的存儲器尤為適用。調試過程中,直接將程序代碼通過C542寫入FLASH中,重新上電后C542即可按照FLASH的方式執行Bootloader 操作,極大的降低了硬件系統調試的難度。

本系統采用8位并行加載。C542復位期間檢查MP/MC引腳是否為低電平,若不是,則從外部程序存儲器0FF80h起執行用戶程序;若是,則從片內 ROM的0FF80h起執行程序。啟動制造商在ROM的自舉加載器程序時,首先應進行初始化,然后檢查INT2引腳,若有效,則從HPI-RAM自舉加載;若無效,則使I/O口選通信號IS為低電平,從地址為0FFFFh的I/O口讀入自舉程序選擇字(BRS)。BRS的低8位決定了自舉加載的方式,若 BRS的低2位為01,則為8位并行加載,然后自舉加載器依據FLASH的地址(BRS中的高6位 + 0000000000)就可讀取自舉表了。自舉加載器將FLASH中的程序代碼全部送到程序存儲器之后,立即轉移到目的地址,并開始執行程序代碼。

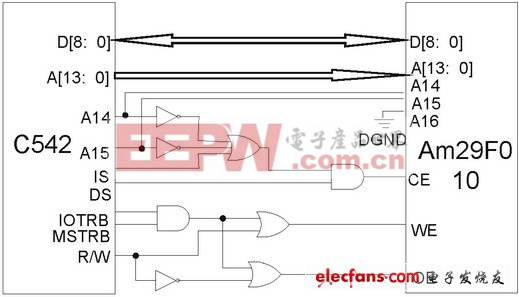

本設計中FLASH芯片選用的是AMD公司的Am29F010,該芯片容量為1Mbit。因為C542只能尋址64K 地址,所以Am29F010的A16引腳接地。

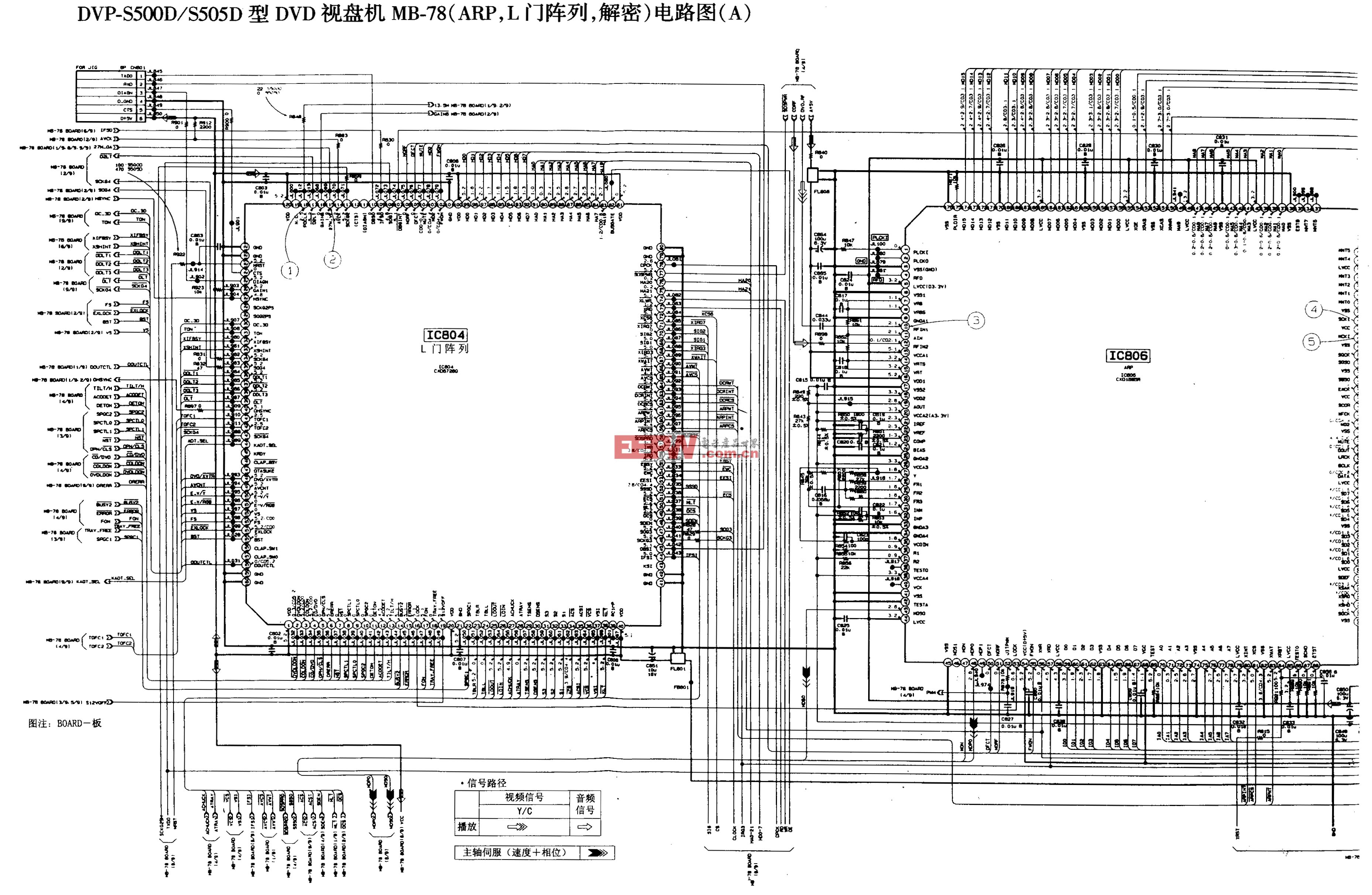

DSP在線加載系統的硬件設計如圖2所示。設計時沒有讓DS直接接CE,而是先讓A14、A15分別接一個非門,這兩個非門的輸出端和IS一起接到一個或門上,此或門的輸出端和DS一起接一個與門,與門的輸出端再接CE。這樣設計使Am29F010的48K至64K地址空間成為數據和I/O復用空間,自舉加載時可從Am29F010的地址為0FFFFh的I/O口讀入自舉程序選擇位。

圖2 DSP在線加載硬件設計圖

ADC設計

根據本系統對ADC分辨率為16位、轉換速率大于125KSPS、低功耗的要求,決定選用ADI公司的AD976A。該芯片具有16位的分辨率,轉換速率為200KSPS,工作電壓為+5V,最大功耗僅為100mW。

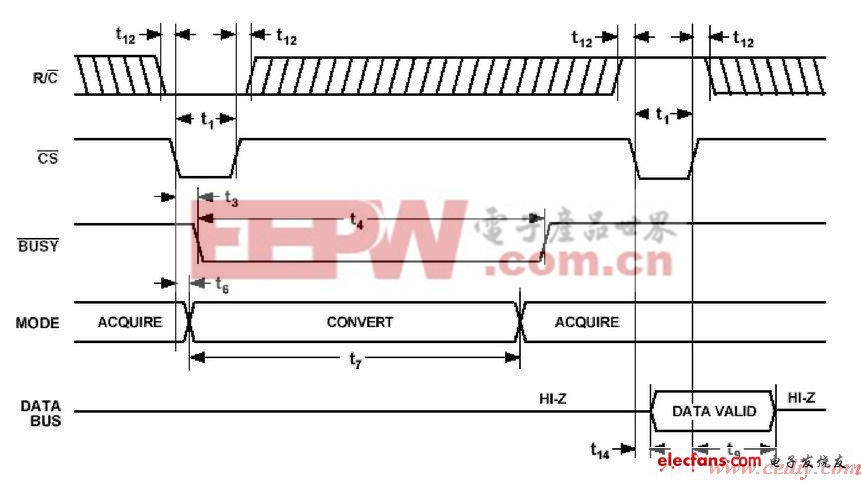

對AD976A的轉換控制和數據的輸出主要涉及到R/C、CS和BUSY三個引腳。AD976A提供了兩種轉換模式:一種是CS一直為低電平,ADC和 DSP讀數據僅由R/C控制;另一種是ADC和DSP讀數據由CS和R/C共同控制。由于C542不能讓ADC的片選信號一直處于選中狀態,所以只有選用第二種模式,如圖3所示。AD976A在CS的下降沿而R/C又為低電平時開始模數轉換,在CS的下降沿而R/C又為高電平時把數據送到數據總線。 BUSY信號在模數轉換開始時變為低電平,結束時變為高電平。

圖3 AD976A轉換模式二圖

進行轉換時, C542首先經過CPLD內部的組合和時序邏輯電路,向AD976A發兩個低電平脈沖R/C和CS,其中R/C脈沖寬度為166.7ns,CS脈沖寬度為 83.3ns ,CS的下降沿在R/C的下降沿之后41.7ns,而上升沿卻在R/C的上升沿之前41.7ns。由于這時CS為下降沿,R/C為低電平,所以 AD976A開始采集數據、進行ADC,BUSY信號也隨之變為低電平。轉換結束,BUSY變為高電平,經過CPLD的邏輯電路后接到C542的INT2 引腳,引起C542中斷。C542接收到中斷后經CPLD向AD976A發一個CS脈沖,由于這時的CS為下降沿,R/C為高電平,所以AD976A把數據放到數據總線上,C542開始讀總線上的數據。

CPLD邏輯電路設計

CPLD是整個系統的控制邏輯電路部分。在CPLD內要實現的主要功能為:

① 產生AD_TRIG同步脈沖

當發聲晶體發聲后,八個DSP就要同時采集數據,AD_TRIG脈沖就是解決“發聲”與“采集”的同步問題以及八個DSP的“采集”同步問題的。

AD_TRIG脈沖的周期是由主CPU決定,由DSP1寫入CPLD。其它七個DSP不向CPLD寫入AD_TRIG脈沖的周期,它們只是AD_TRIG脈沖的接收者。

② 產生控制ADC的R/C和CS信號

R/C和CS信號是在AD_TRIG同步脈沖的基礎上產生的。在產生R/C和CS的時序邏輯電路中,有些觸發器的時鐘就是AD_TRIG脈沖,這樣八個DSP的采集、轉換就被同步。

③ 產生FIRE點火脈沖

FIRE點火脈沖是在CPLD內產生的使發射晶體發聲的脈沖。當DSP1 接到主CPU傳來的采集數據的命令時,就向CPLD發出產生FIRE脈沖的命令,CPLD經其內部組合和時序邏輯電路產生FIRE脈沖,然后送往主 CPU,主CPU接到該脈沖后向發射模塊發命令,使發射晶體發聲。在設計時,產生FIRE脈沖的時序邏輯電路的有些觸發器也是以AD_TRIG脈沖為時鐘的,這樣就解決了發聲晶體“發聲”與DSP“采集”的同步問題。

④ 作為DSP與主CPU之間的通信接口

主CPU的命令要傳給DSP,八個DSP最后處理過的數據也要傳給主CPU,因此,在CPLD中設計了一個同步串口。設計此串口要注意的是當DSP向主 CPU傳送數據時八個DSP不能發生沖突。下面的VHDL程序是本設計中對這一問題的解決,其中bfsx1~bfsx8是DSP1~DSP8的發送幀同步脈沖,bdx1~bdx8是DSP1~DSP8的緩沖串行口數據發送端發送的數據,fsx、dx是從CPLD輸出的發送幀同步脈沖和發出的數據。

fsx《= bfsx1 and bfsx2 and bfsx3 and bfsx4 and bfsx5 and bfsx6 and bfsx7 and bfsx8;

評論