概述學(xué)習(xí)FPGA的一些常見誤區(qū)

1、不熟悉FPGA的內(nèi)部結(jié)構(gòu),不了解可編程邏輯器件的基本原理。

FPGA為什么是可以編程的?恐怕很多菜鳥不知道,他們也不想知道。因?yàn)樗麄冇X得這是無關(guān)緊要的。他們潛意識(shí)的認(rèn)為可編程嘛,肯定就是像寫軟件一樣啦。軟件編程的思想根深蒂固,看到Verilog或者VHDL就像看到C語言或者其它軟件編程語言一樣。一條條的讀,一條條的分析。如果這些菜鳥們始終拒絕去了解為什么 FPGA是可以編程的,不去了解FPGA的內(nèi)部結(jié)構(gòu),要想學(xué)會(huì)FPGA恐怕是天方夜譚。雖然現(xiàn)在EDA軟件已經(jīng)非常先進(jìn),像寫軟件那樣照貓畫虎 也能綜合出點(diǎn)東西,但也許只有天知道EDA軟件最后綜合出來的到底是什么。也許點(diǎn)個(gè)燈,跑個(gè)馬還行。這樣就是為什么很多菜鳥學(xué)了N久以后依然是一個(gè)菜鳥的原因。

那么FPGA為什么是可以“編程”的呢?

首先來了解一下什么叫 “程”。其實(shí)“程”只不過是一堆具有一定含義的01編碼而已。編程,其實(shí)就是編寫這些01編碼。只不過我們現(xiàn)在有了很多開發(fā)工具,通常都不是直接編寫這些 01編碼,而是以高級(jí)語言的形式來編寫,最后由開發(fā)工具轉(zhuǎn)換為這種01編碼而已。對(duì)于軟件編程而言,處理器會(huì)有一個(gè)專門的譯碼電路逐條把這些01編碼翻譯為各種控制信號(hào),然后控制其內(nèi)部的電路完成一個(gè)個(gè)的運(yùn)算或者是其它操作。所以軟件是一條一條的讀,因?yàn)檐浖牟僮魇且徊揭徊酵瓿傻摹6鳩PGA的可編程,本質(zhì)也是依靠這些01編碼實(shí)現(xiàn)其功能的改變,但不同的是FPGA之所以可以完成不同的功能,不是依靠像軟件那樣將01編碼翻譯出來再去控制一個(gè)運(yùn)算電路,F(xiàn)PGA里面沒有這些東西。

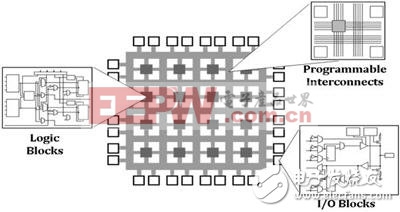

FPGA內(nèi)部主要三塊:可編程的邏輯單元、可編程的連線和可編程的IO模塊。

可編程的邏輯單元是什么?其基本結(jié)構(gòu)某種存儲(chǔ)器(SRAM、FLASH等)制成的4輸入或6輸入1輸出地“真值表”加上一個(gè)D觸發(fā)器構(gòu)成。任何一個(gè)4輸入1輸出組合邏輯電路,都有一張對(duì)應(yīng)的“真值表”,同樣的如果用這么一個(gè)存儲(chǔ)器制成的4輸入1輸出地“真值表”,只需要修改其“真值表” 內(nèi)部值就可以等效出任意4輸入1輸出的組合邏輯。這些“真值表”內(nèi)部值是什么?就是那些01編碼而已。如果要實(shí)現(xiàn)時(shí)序邏輯電路怎么辦?這不又D觸發(fā)器嘛, 任何的時(shí)序邏輯都可以轉(zhuǎn)換為組合邏輯+D觸發(fā)器來完成。但這畢竟只實(shí)現(xiàn)了4輸入1輸出的邏輯電路而已,通常邏輯電路的規(guī)模那是相當(dāng)?shù)拇笈丁D窃趺崔k呢?這個(gè)時(shí)候就需要用到可編程連線了。在這些連線上有很多用存儲(chǔ)器控制的鏈接點(diǎn),通過改寫對(duì)應(yīng)存儲(chǔ)器的值就可以確定哪些線是連上的而哪些線是斷開的。這就可以把很多可編程邏輯單元組合起來形成大型的邏輯電路。最后就是可編程的IO,這其實(shí)是FPGA作為芯片級(jí)使用必須要注意的。任何芯片都必然有輸入引腳和輸出引腳。有可編程的IO可以任意的定義某個(gè)非專用引腳(FPGA中有專門的非用戶可使用的測(cè)試、下載用引腳)為輸入還是輸出,還可以對(duì)IO的電平標(biāo)準(zhǔn)進(jìn)行設(shè)置。

總歸一句話,F(xiàn)PGA之所以可編程是因?yàn)榭梢酝ㄟ^特殊的01代碼制作成一張張“真值表”,并將這些“真值表”組合起來以實(shí)現(xiàn)大規(guī)模的邏輯功能。不了解FPGA內(nèi)部結(jié)構(gòu),就不能明白最終代碼如何變到FPGA里面去的。也就無法深入的了解如何能夠充分運(yùn)用FPGA。現(xiàn)在的FPGA,不單單是有前面講的那三塊,還有很多專用的硬件功能單元,如何利用好這些單元實(shí)現(xiàn)復(fù)雜的邏輯電路設(shè)計(jì),是從菜鳥邁向高手的路上必須要克服的障礙。而這一切,還是必須先從了解 FPGA內(nèi)部邏輯及其工作原理做起。

2、錯(cuò)誤理解HDL語言,怎么看都看不出硬件結(jié)構(gòu)。

HDL語言的英語全稱是:Hardware Description Language,注意這個(gè)單詞Description,而不是Design。老外為什么要用Description這個(gè)詞而不是Design呢?因?yàn)?HDL確實(shí)不是用用來設(shè)計(jì)硬件的,而僅僅是用來描述硬件的。

描述這個(gè)詞精確地反映了HDL語言的本質(zhì),HDL語言不過是已知硬件電路的文本表現(xiàn)形式而已, 只是將以后的電路用文本的形式描述出來而已。而在編寫語言之前,硬件電路應(yīng)該已經(jīng)被設(shè)計(jì)出來了。語言只不過是將這種設(shè)計(jì)轉(zhuǎn)化為文字表達(dá)形式而已。但是很多人就不理解了,既然硬件都已經(jīng)被設(shè)計(jì)出來了,直接拿去制作部就完了,為什么還要轉(zhuǎn)化為文字表達(dá)形式再通過EDA工具這些麻煩的流程呢?其實(shí)這就是很多菜鳥沒有了解設(shè)計(jì)的抽象層次的問題,任何設(shè)計(jì)包括什么服裝、機(jī)械、廣告設(shè)計(jì)都有一個(gè)抽象層次的問題。就拿廣告設(shè)計(jì)來說吧,最初的設(shè)計(jì)也許

評(píng)論