基于FPGA的SPI Flash控制器的設計方案

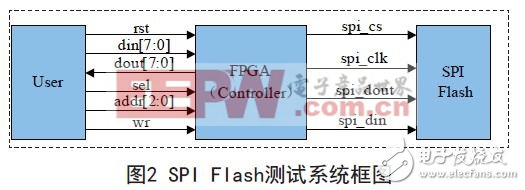

SPI Flash控制器由VHDL編寫,主要為SPIFlash芯片提供串行時鐘,將從用戶端輸入的數據(包括指令字節、地址字節和數據字節)寄存起來并在串行時鐘的控制下通過spi_dout信號線逐位輸出到SPI Flash芯片中,同樣將從SPI Flash芯片中讀出的串行數據轉換成并行數據送給用戶端。此外,SPI Flash控制器還必須在用戶通過sel、addr以及wr組合發出的操作命令下產生一系列的控制信號,并在這些控制信號的作用下根據狀態機的轉換方向進行動作并且輸出相應的結果。

3.2 SPI Flash控制器控制狀態機

由于SPI Flash操作命令較多,并且很多操作命令之間存在相同的操作步驟,所以利用狀態機進行控制能夠準確有條理地完成對SPI Flash的操作。分析GDQ25系列SPI Flashdatasheet,可將SPI Flash控制器的工作狀態劃分為空閑狀態(IDLE)、傳輸指令狀態(TxCMD)、傳輸高字節地址狀態(TxADD_H)、傳輸中間字節地址狀態(TxADD_M)、傳輸低字節地址狀態(TxADD_L)、傳輸偽字節狀態(TxDummy)、傳輸數據狀態(TxDATA)和接收數據狀態(RxDATA)。除此以外,由于所有接收到的指令值都寄存在指令寄存器內,當一條指令執行完畢時需要將指令寄存器清空,以便接收下一條用戶指令,所以設定一個清除指令狀態(CLR_CMD)作為每一操作完成后的收尾狀態。當狀態機進入CLR_CMD狀態后,表示當前操作已經完成,正將指令寄存器指令值清空;當狀態機進入IDLE狀態時,用戶可輸入下一操作指令,對SPI Flash進行下一操作。考慮到SPI Flash的響應時間,在以上工作狀態中間插入了一些等待狀態(WAIT)。

4.SPI Flash控制器驗證

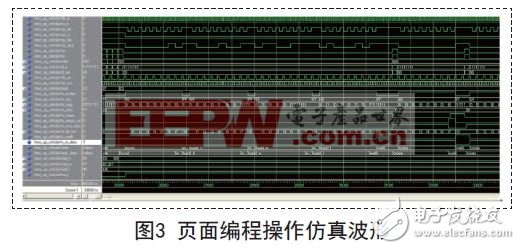

SPI Flash控制器IP核在Modelsim 6.5g上能夠通過功能仿真,下面分析一下SPI Flash頁面編程操作及數據讀取操作的功能仿真。

4.1 頁面編程操作

頁面編程操作仿真波形如圖3所示,圖中截取輸入00H和01H數據的波形,最多可連續輸入一頁 256字節數據。當用戶輸入頁面編程指令02H,狀態機進入txcmd狀態,頁編程指令02H通過spi_dout傳輸給SPI Flash.當tx_bit_cnt計數到8時,指令傳輸完畢,狀態機在等待后進入txadd_h狀態,同時tx_bit_cnt被清零,需寫入數據的對應存儲空間的起始地址高字節值89H被傳輸。當tx_bit_cnt計數到8時,高字節地址值89H被傳輸完畢,狀態機在等待后進入txadd_m狀態,同時tx_bit_cnt被清零,同上,地址中間字節67H和45H被傳輸。當add_h、add_m和add_l寄存器的值依次傳輸完畢,狀態機進入 wait6狀態,等待用戶輸入需寫入SPI Flash的數據。當用戶設定{sel,addr,wr}為10001b,狀態機進入txdata狀態,同時tx_new_data被置高,表示要傳輸新寫入的數據。在txdata狀態下,控制器將傳輸寫入的第1字節數據00H,當tx_bit_cnt計數到8時,第1字節數據00H被傳輸完畢,tx_new_data被拉低,tx_empty被拉高,表示當前沒有可傳輸的數據,狀態機進入wait6狀態,等待新數據寫入。直到用戶再次設定 {sel,addr,wr}為10001b,狀態機再次進入txdata狀態,同時tx_new_data被置高,表示寫入的第2字節數據01H將要傳輸。當tx_bit_cnt計數到8,第2字節數據傳輸完畢,tx_new_data被拉低,tx_empty被拉高,狀態機進入wait6狀態。由于 GDQ25系列SPI Flash頁面編程一次最多可寫入256字節數據,所以用戶在寫入數據時,應注意最多寫入256次數據,否則超過的數據將覆蓋開始的數據。當狀態機處于 wait6狀態而用戶想結束頁面編程時,可向控制器輸入NOP指令強制結束當前頁面編程操作。狀態機在接收到NOP指令后將進入clr_cmd狀態和 idle空閑態,等待下一條指令的到來。當頁面編程操作還沒結束時,busy將一直被置高。

4.2 數據讀取操作

讀數據指令仿真波形如圖4所示。當用戶輸入讀數據指令03H,狀態機進入txcmd狀態,讀數據指令通過spi_dout傳輸給SPI Flash。

當tx_bit_cnt計數到8時,指令傳輸完畢,狀態機等待后進入txadd_h狀態,傳輸要讀出數據所在存儲空間起始地址的高字節,同時tx_bit_cnt清零,以為下一個傳

fpga相關文章:fpga是什么

評論