24位Σ-Δ ADC簡化ECG/EKG模擬前端設計

4、低通/抗混疊濾波器

低通濾波器用來抑制高頻干擾,它也作為一個抗混疊濾波器(即阻止任何大于奈奎斯特或1 / 2采樣頻率的信號,避免產生ADC混疊)。

為了進一步降低輸入共模信號,ECG設計通常還引入一級“右腿驅動器”,驅動反相共模信號返回人體。為了確保病人的安全,通常利用一個運算放大器和一個限流電阻,確保驅動到人體的是一個非常微弱的信號源。這個屏蔽裝置旨在降低ECG探頭承載信號的噪聲耦合。

總之,ECG應用中的有用信號小于100mV,考慮到失調和共模信號,通常將其放大到2V。因此,AFE必須有2V測量范圍,可以辨識低于幾百,甚至幾十μV的信號,采樣率在1ksps左右。

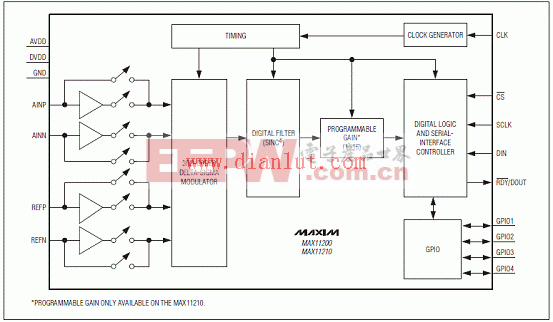

正確的ADC可以減少、甚至消除對AFE的需求

AFE設計完成后,能夠滿足實際應用對分辨率、速率和輸入量程的要求的ADC有許多。但是,仍要優先考慮具有高分辨率、高共模抑制比(CMRR)及其它優勢的ADC,以確保ECG的設計需求。

MAX11040K同步采樣、Σ-ΔADC本身的性能指標即超出了此類應用的最低要求,可以取代系統的大部分功能電路,甚至可以省去AFE,提供了一種更可靠、更小封裝、更簡便的設計方案。

MAX11040K具備才應用的幾項必備規格:

![]() 輸入量程:±2.2V

輸入量程:±2.2V

![]() 差分輸入

差分輸入

![]() 110dB共模抑制比(典型值)

110dB共模抑制比(典型值)

![]() 24位分辨率:

24位分辨率:

SNR >110dB

19位無噪聲范圍

有效分辨率 = 2/219 = 3.8μV

![]() ±6V輸入過壓保護

±6V輸入過壓保護

![]() 四路全差分同步采樣ADC

四路全差分同步采樣ADC

可級聯多達32個通道同步采樣

![]() 可編程輸出數據速率

可編程輸出數據速率

模擬信號相關文章:什么是模擬信號

濾波器相關文章:濾波器原理

濾波器相關文章:濾波器原理

高通濾波器相關文章:高通濾波器原理

評論