如何解決FPGA電路設計中的毛刺問題

引言

本文引用地址:http://www.104case.com/article/20548.htm隨著半導體技術的飛速發展,fpga(field programmable gate array)的計算能力、容量以及可靠性也有了很大的提高。它正以高度靈活的用戶現場編程功能、靈活的反復改寫功能、高可靠性等優點,成為數字電路設計、數字信號處理等領域的新寵。但和所有的數字電路一樣,毛刺也是fpga電路中的棘手問題。它的出現會影響電路工作的穩定性、可靠性,嚴重時會導致整個數字系統的誤動作和邏輯紊亂。因此,如何有效正確的解決設計中出現的毛刺,就成為整個設計中的關鍵一環。

本文就fpga設計中出現的毛刺問題,根據筆者自己的經驗和體會,提出了幾種簡單可行的解決方法和思路,供同行供交流與參考。

fpga電路中毛刺的產生

我們知道,信號在fpga器件中通過邏輯單元連線時,一定存在延時。延時的大小不僅和連線的長短和邏輯單元的數目有關,而且也和器件的制造工藝、工作環境等有關。因此,信號在器件中傳輸的時候,所需要的時間是不能精確估計的,當多路信號同時發生跳變的瞬間,就產生了“競爭冒險”。這時,往往會出現一些不正確的尖峰信號,這些尖峰信號就是“毛刺”。另外,由于fpga以及其它的cpld器件內部的分布電容和電感對電路中的毛刺基本沒有什么過濾作用,因此這些毛刺信號就會被“保留”并傳遞到后一級,從而使得毛刺問題更加突出。

可見,即使是在最簡單的邏輯運算中,如果出現多路信號同時跳變的情況,在通過內部走線之后,就一定會產生毛刺。而現在使用在數字電路設計以及數字信號處理中的信號往往是由時鐘控制的,多數據輸入的復雜運算系統,甚至每個數據都由相當多的位數組成。這時,每一級的毛刺都會對結果有嚴重的影響,如果是多級的設計,那么毛刺累加后甚至會影響整個設計的可靠性和精確性。下面我們將以乘法運算電路來說明毛刺的產生以及去除,在實驗中,我們使用的編程軟件是quartus ii2.0,實驗器件為cyclone ep1cf400i7。需要說明一點,由于示波器無法顯示該整數運算的結果,我們這里將只給出軟件仿真的結果。而具體的編程以及程序的下載我們在這里也不再詳述,可以參考相關的文獻書籍。

毛刺的消除方法

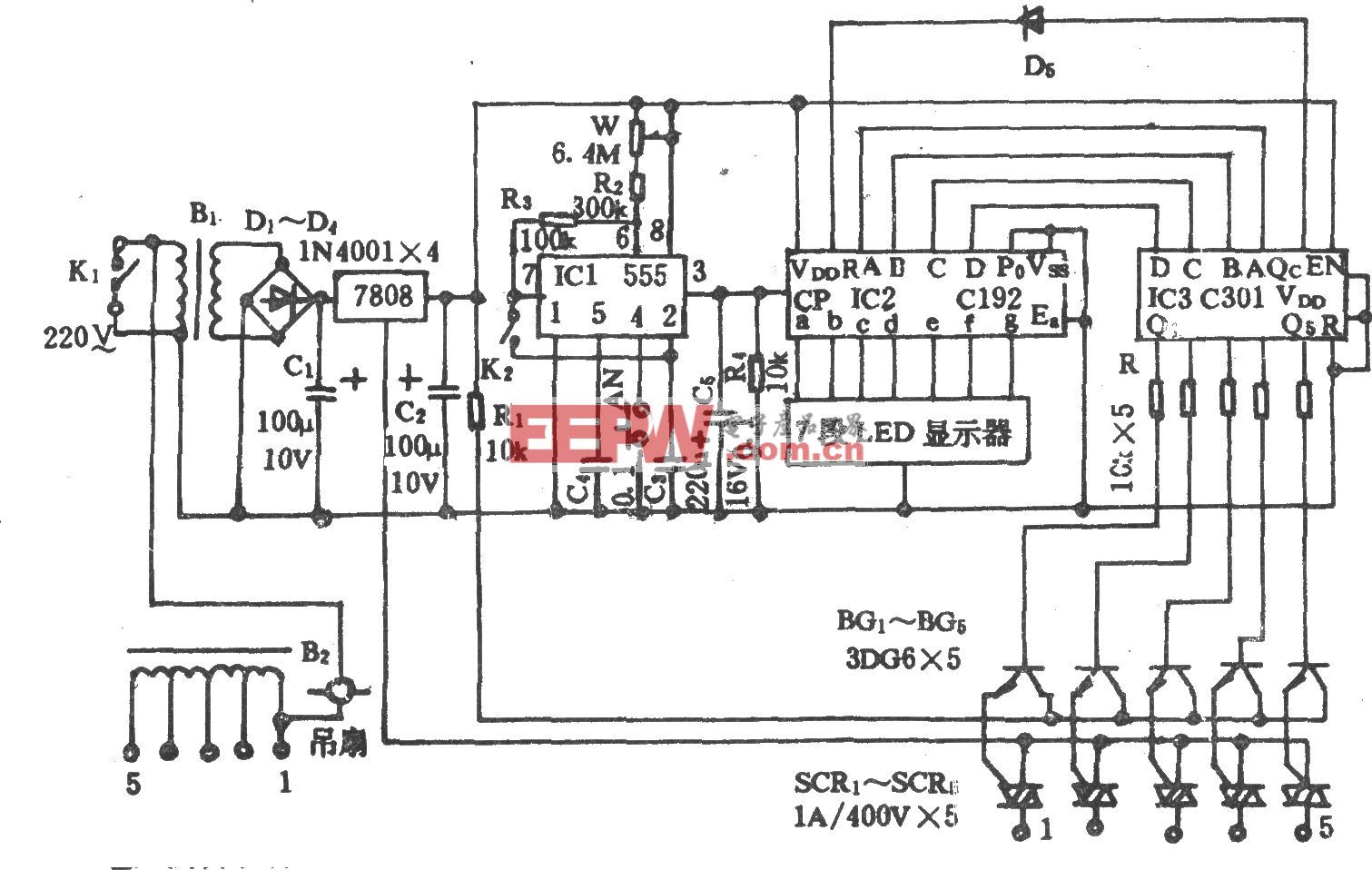

首先,我們來設計一個簡單的乘法運算電路。運算電路如圖1所示。

圖 1 乘法運算運算電路及結果

如圖1(c)所示,如果在不加任何的去除毛刺的措施的時候,我們可以看到結果c中含有大量的毛刺。產生的原因就是在時鐘的上升沿,每個輸入(a和b)的各個數據線上的數據都不可能保證同時到達,也就是說在時鐘讀取數據線上的數據的時候,有的數據線上讀取的已經是新的數據,而有的數據線上讀取的仍然是上一個數據,這樣無疑會產生毛刺信號,而當數據完全穩定的時候,毛刺信號也就自然消失了。

輸出加d觸發器

這是一種比較傳統的去除毛刺的方法。原理就是用一個d觸發器去讀帶毛刺的信號,利用d觸發器對輸入信號的毛刺不敏感的特點,去除信號中的毛刺。這種方法在簡單的邏輯電路中是常見的一種方法,尤其是對信號中發生在非時鐘跳變沿的毛刺信號去除效果非常的明顯。

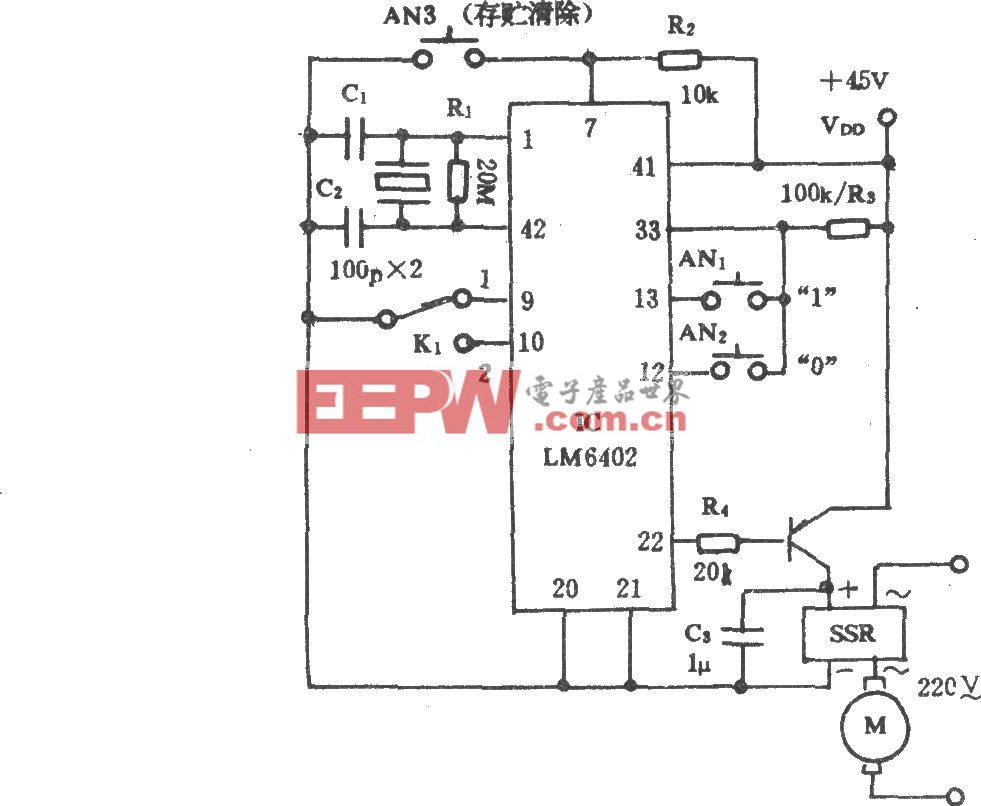

但是對于大多數的時序電路來說,毛刺信號往往發生在時鐘信號的跳變沿,這樣d觸發器的效果就沒有那么明顯了(見圖2,加d觸發器以后的輸出q,仍含有毛刺)。另外,d觸發器的使用還會給系統帶來一定的延時,特別是在系統級數較多的情況下,延時也將變大,因此在使用d觸發器去除毛刺的時候,一定要視情況而定,并不是所有的毛刺都可以用d觸發器來消除。

圖2 加d觸發器后的運算電路及結果

信號同步法

在很多文章中都提到,設計數字電路的時候采用同步電路可以大大減少毛刺。另外,由于大多數毛刺都比較短(大概幾個納秒),只要毛刺不出現在時鐘跳變沿,毛刺信號就不會對系統造成危害了。因此很多人認為,只要在整個系統中使用同一個時鐘就可以達到系統同步的目標了。但是這里面有一個非常嚴重的問題,就是時鐘信號和其他所有的信號一樣,在fpga器件中傳遞的時候是有延時的,這樣根本就無法預知時鐘跳變沿的精確位置。也就是說我們無法保證在某個時鐘的跳變沿讀取的數據是一個穩定的數據,尤其是在多級設計中,這個問題就更加突出了。因此,做到真正的"同步"就是去除毛刺信號的關鍵問題。我認為這里同步的關鍵就是保證在時鐘的跳變沿讀取的數據是穩定的數據而不是毛刺數據。以這個思想為出發點,提出了以下幾種具體的信號同步方法。

信號延時同步法

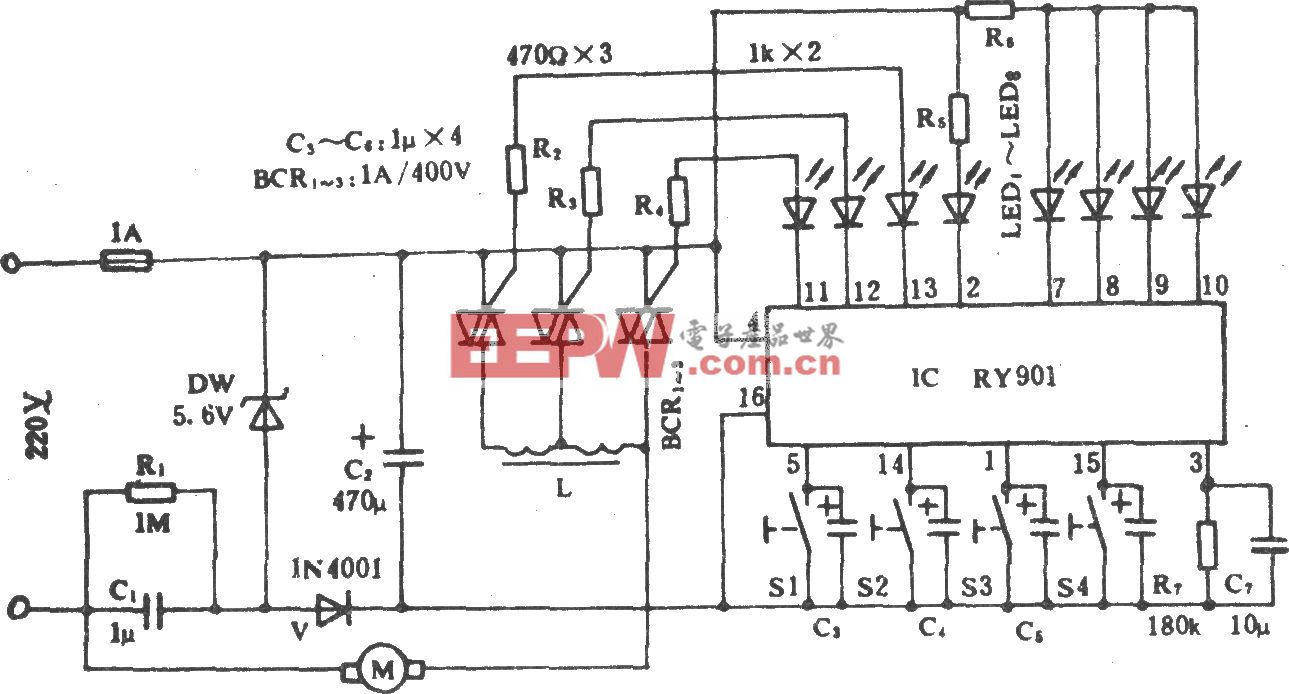

首先,我們給出了一個兩級乘法(c=a b;q=d c)的運算結果(如圖3所示,這里不再給出運算電路)。可以看到,在沒加任何處理過程的時候,兩級結果c和q中都含有大量的毛刺信號。其中毛刺信號產生的原因就是在計算時鐘跳變時刻,數據信號同時發生了跳變。另外,第一級信號c中含有大量的毛刺,在經過第二次乘法運算以后被明顯放大了,從圖3可以看出q中毛刺更加嚴重了。但在很多實際工作中,我們最關心的往往是最后的輸出結果(q),只要中間信號的毛刺對后面的輸出沒有什么影響我們就不需要對它們作任何處理了。因此,這里所提出的信號同步的核心思想就是消除這些中間毛刺信號的影響。

圖 3 兩級乘法運算的結果仿真

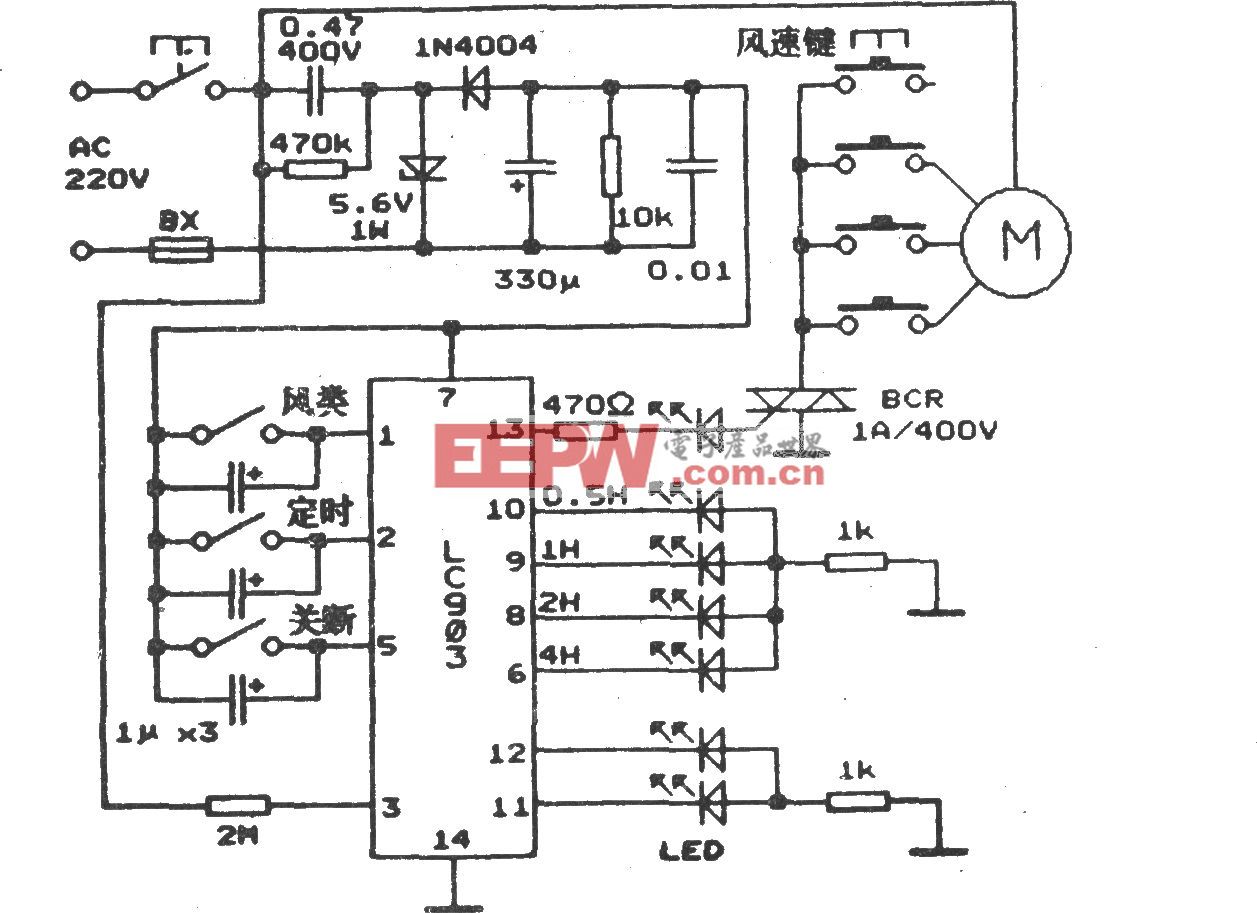

信號延時法,它的原理就是在兩級信號傳遞的過程中加一個延時環節,從而保證在下一個模塊中讀取到的數據是穩定后的數據,即不包含毛刺信號。這里所指的信號延時可以是數據信號的延時,也可以是時鐘信號的延時。由于篇幅的關系,這里我們主要以對時鐘信號的延時來說明信號延時法的原理。對上述計算過程加時鐘信號延時的原理及結果如圖4所示。

圖4 加了時鐘延時的兩級乘法運算及結果

圖4中的clkdelay就是時鐘延時環節。在加這個環節以前的時鐘信號是直接連到模塊b上的,這樣兩個模塊使用同一時鐘,好像已經做到了同步,但是如圖3所示,結果中含有大量的毛刺,其原因就是產生毛刺的根本原因--“競爭冒險"現象沒有得到根本性的消除。加時鐘延時環節的作用就是要從根本上消除“競爭冒險”,其過程是將控制模塊b的時鐘延時一段時間,使得模塊b的控制時鐘在上跳變化時數據c已經達到了穩定,即不含毛刺信號的數據,而這時數據d也已達到穩定,這樣競爭冒險現象消除了,從而毛刺信號也得到了有效的抑制,如圖4 (c) 所示。

與時鐘延時法的原理相同,我們也可以在數據信號加延時環節來消除競爭冒險的現象,達到真正的同步。這里的延時環節可以使用quartus ⅱ提供的lcell實現,也可以使用d觸發器和一個高頻的計數脈沖靈活實現。另外我們也可以從綜合結果(圖4 (c)所示)看到,所加的延時環節占用的芯片資源是很少的,是一種簡單有效而且節約資源的方法。

時鐘信號的靈活使用

和上述方法的原理相似,靈活使用時鐘信號的目的也是盡可能的消除競爭冒險。比如在時鐘的第一個跳變沿觸發模塊a,下一個跳變沿控制觸發模塊b,這樣時鐘的交替控制也在一定程度上消除了競爭冒險,從而抑制了毛刺信號。還比如分別使用時鐘的上升沿或者下降沿控制不同的模塊。但是這些方法不適合使用在比較復雜的設計中,否則會使設計的條理非常的混亂,給以后的閱讀修改帶來很大的困難。因此,在選用這種方法的時候一定要慎重。

狀態機控制

對于大型的數字電路設計,狀態機是一種非常理想的選擇,能使運行性能和硬件資源的占用達到最佳的優化,另外靈活的使用狀態機也可以實現信號的同步和消除毛刺的目的。在數據傳遞比較復雜的多模塊系統中,由狀態機在特定的時刻分別發出控制特定模塊的時鐘信號或者模塊使能信號,狀態機的循環控制就可以使得整個系統協調運作,同時減少毛刺信號。那么只要我們在狀態機的觸發時間上加以處理,就可以避免競爭冒險,從而抑制毛刺的產生。原理如圖5所示。

圖 5 狀態機控制原理

限于篇幅的原因,這里我們只講述狀態機控制的原理,提出一種新的思路。

總結

由于毛刺信號對fpga器件的運行有很大的影響,如何有效抑制毛刺信號就成了一個非常突出的問題。但是必須強調的一點就是,我們首先必須對程序設計本身進行優化和改進,使毛刺信號的產生降低到最小,比如將一些信號用變量代替來減小延時等。另外,在實際應用中如何選用適合的方法也非常的重要,一定要慎重考慮。比如延時環節的加入會使整個系統的延時增大,加入太多時就會影響系統的運行等。

評論