使用MATLAB和Simulink算法創建FPGA原型

芯片設計和驗證工程師通常要為在硅片上實現的每一行RTL代碼寫出多達10行測試平臺代碼。驗證任務在設計周期內可能會占用50%或更多的時間。盡管如此辛苦,仍有接近60%的芯片存在功能瑕疵,需要返工。由于HDL仿真不足以發現系統級錯誤,芯片設計人員正利用FPGA來加速算法創建和原型設計。

利用FPGA處理大型測試數據集可以使工程師快速評估算法和架構并迅速做出權衡。工程師也可以在實際環境下測試設計,避免因使用HDL仿真器消耗大量時間。系統級設計和驗證工具(如MATLAB和Simulink)通過在FPGA上快速建立算法原型,可以幫助工程師實現這些優勢。

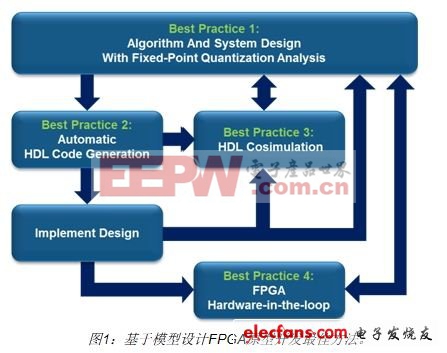

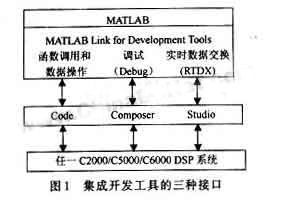

本文將介紹使用MATLAB和Simulink創建FPGA原型的最佳方法。這些最佳方法包括:在設計過程初期分析定點量化的效應并優化字長,產生更小、更高效的實現方案;利用自動HDL代碼生成功能,更快生成FPGA原型;重用具有HDL協同仿真功能的系統級測試平臺,采用系統級指標分析HDL實現方案;通過FPGA在環仿真加速驗證(圖1)。

為什么在FPGA上建立原型?

在 FPGA上建立算法原型可以增強工程師的信心,使他們相信自己的算法在實際環境中的表現能夠與預期相符。除了高速運行測試向量和仿真方案,工程師還可以利用FPGA原型試驗軟件功能以及諸如RF和模擬子系統的相關系統級功能。此外,由于FPGA原型運行速度更快,可以使用大型數據集,暴露出仿真模型未能發現的缺陷。

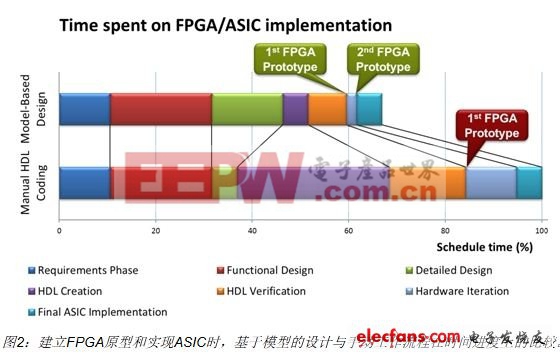

采用HDL代碼生成功能的基于模型的設計可以使工程師有效地建立FPGA原型,如圖2所示。該圖向我們展示了這樣一種現實情況:工程師經常縮短詳細設計階段,試圖通過盡快開始硬件開發階段以符合開發周期的要求。現實中,當工程師發現定點算法達不到系統要求時,就得在 HDL創建階段重新審視詳細設計階段。這樣的重疊工作將使HDL創建階段延長(如紫色長條所示),并可能引發各種設計問題(如膠合邏輯或設計補丁)。

由于自動HDL代碼生成流程比手工編碼快,工程師得以把節省下來的時間投入到詳細設計階段,生成更優質的定點算法。與手動的工作流程相比,這種方法使工程師能夠以更快的速度生成質量更佳的FPGA原型。

數字下變頻器案例研究

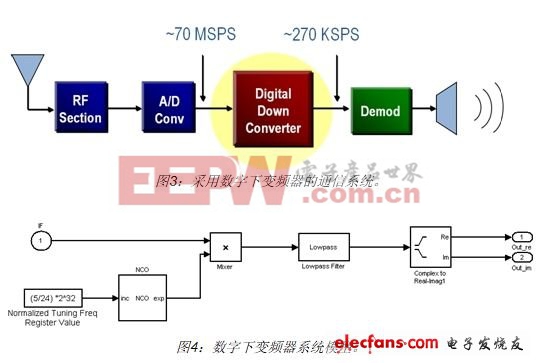

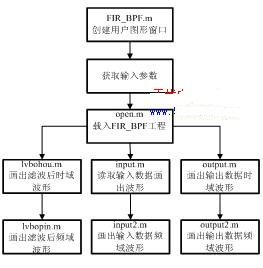

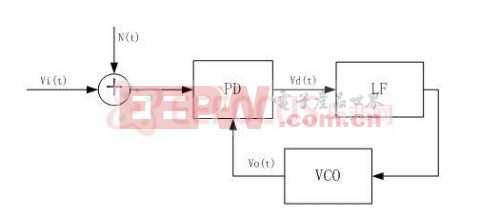

為了說明采用基于模型的設計建立FPGA原型的最佳方法,可借助數字下變頻器(DDC)來進行案例研究。在眾多的通信系統中,DDC是一種普通的構建塊(圖 3)。該構建塊用于將高速通帶輸入轉換為低速基帶輸出,以便使用較低采樣率時鐘進行處理。這樣,在硬件實施階段便可降低功耗、節約資源。DDC的主要部件包括:數控振蕩器(NCO)、混頻器和數字濾波器鏈路(圖4)。

在設計過程初期分析定點量化的效應

工程師通常使用浮點數據類型來測試新的構想和開發初始算法。然而,FPGA和 ASIC硬件實現要求轉換為定點數據類型,而這往往會造成量化誤差。使用手動工作流程時,通常在HDL編碼過程中執行定點量化。在該工作流程中,工程師無法輕易地通過比較定點表示形式和浮點參考值量化定點量化的效應,而分析針對溢出的HDL實現也同樣不易。

評論