基于FPGA的FIR數字濾波器設計方案(二)

3.3 數字濾波器的ModelSim功能仿真

ModelSim軟件可支持VHDL和Verilog混合仿真,無論是FPGA設計的RTL級和門級電路仿真,還是系統的功能仿真都可以用ModelSim來實現[4-5]。由Signal Com-piler生成的Verilog硬件描述語言模塊,在ModelSim中可以直接對Verilog代碼進行仿真,檢測源代碼是否符合功能要求。圖 10所示的16階FIR數字濾波器的功能仿真結果圖。與圖8的Simulink仿真結果圖的波形一致,表明經過轉換的Verilog源代碼可以實現正常的濾波功能。

FIR數字濾波器一般是嵌入在采集器的采集板卡中進行工作的,把由數字濾波器的Verilog源代碼生成的模塊嵌入到采集板卡的FPGA邏輯中,如圖11所示。

在Quartus Ⅱ環境下,數字濾波器的內部邏輯經過編譯適配之后,以。sof文件的形式直接加載到FPGA中。

4 FIR 數字濾波器的FPGA 實時測試

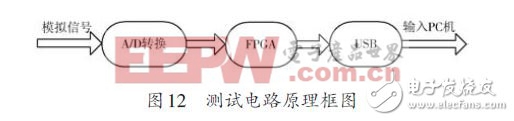

進行實時測試的電路是應用FPGA和USB的數據采集電路,如圖12所示。

測試時把信號發生器設置好的輸入信號輸入到A/D,采樣得到的數據經過FPGA,再通過USB與PC機相連,應用QuartusⅡ中的SignalTapⅡ工具進行實時檢測,結果如圖13所示,其中,上面的波形為輸入波形,頻率為200 Hz,下面的波形為輸出波形,由于200 Hz在低通的帶通內,所以兩者的波形相差不大。當輸入波形為頻率533 Hz時,由于是在截頻點,其輸出波形的幅值約為輸入波形幅值的71%,如圖13和14所示。

5 結束

FIR數字濾波器在數字信號處理領域有著廣泛的使用,本文通過仿真和實時驗證兩種方式實現了一種基于FPGA和DSP Builder的FIR數字濾波器。先根據FIR濾波器的基本原理和結構框圖搭建了濾波器的模型,再根據濾波器的性能指標通過FDATool工具對其進行設計,并通過系統級仿真和ModelSim功能仿真進行了簡要的可行性分析,最后通過QuartusⅡ軟件對FIR數字濾波器進行實時驗證,表明本

評論