Xilinx Spartan-3系列FPGA的配置電路

這里要談的是Xilinx的spartan-3系列FPGA的配置電路。當然了,其它系列的FPGA配置電路都是大同小異的,讀者可以類推,重點參考官方提供的datasheet,畢竟那才是最權威的資料。

所謂典型,這里要列出一個市面上最常見的spartan-3的xc3s400的配置電路。所有spartan-3的FPGA配置電路的鏈接方式都是一樣的。Xc3s400是40萬門FPGA,它的Configuration Bitstream雖然只有1.699136Mbit,但是它還是需要2Mbit的配置芯片XCF02S,不能想當然的以為我的設計簡單,最多用到1Mbit,那么我選XCF01S(1Mbit)就可以了。事實并非如此,即使你只是用xc3s400做一個流水燈的設計,那么你下載到ROM(XCF02S)里的數據也是1.699136Mbit的,所以對于FPGA的配置ROM的選擇宜大不宜小。

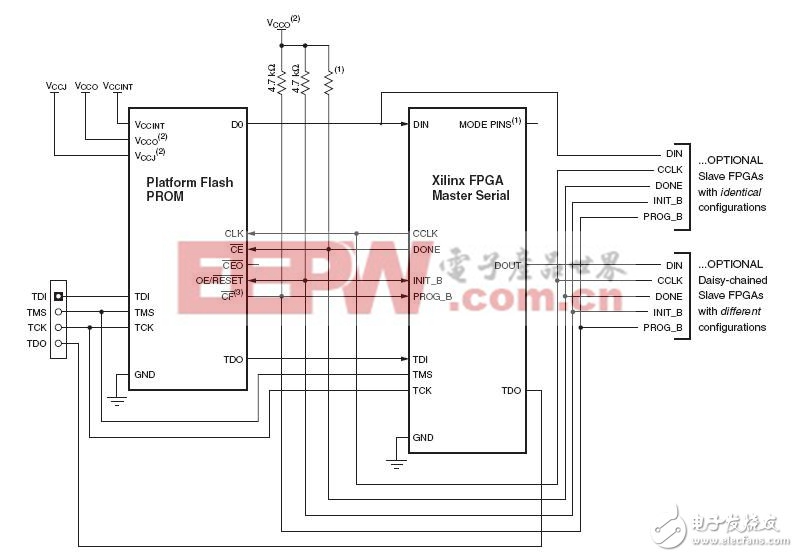

配置電路無非有下面五種:主串,從串,主并,從并,JTAG。前四種是相對于下載到PROM而言的(串并是相對于不同配置芯片是串口和時并口協議和FPGA通訊區分的),只有JTAG是相對于調試是將配置下載到FPGA的RAM而言的(掉電后丟失)。FPGA和CPLD相比,CPLD是基于ROM型的,就是在數據下載到CPLD上,掉電后不丟失。而FPGA則是基于RAM的,如果沒有外部ROM存儲配置數據,那么掉電后就丟失數據。所以FPGA都需要外接有配置芯片(當然現在也有基于FLASH的FPGA出現)。那么我們就來看一下主串模式下FPGA的配置電路的連接。

官方的硬件連接如下:

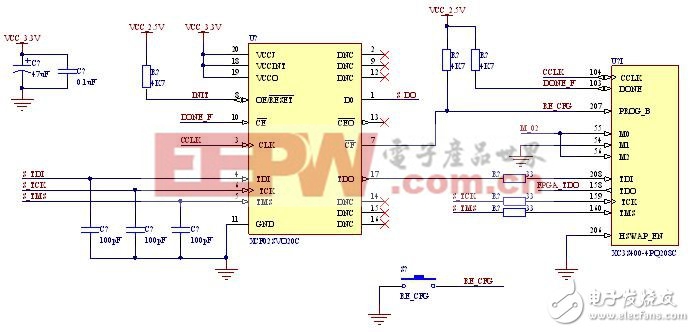

為了增加配置電路的可靠性,通常我們我們增加一些抗干擾的設計(如增加濾波電容、匹配電阻):

先看PROM芯片的各個管腳吧。18,19,20腳就不談了,根據datasheet給供相對應的電平;3腳CLK是接了FPGA的CCLK,數據通信的同步就是通過FPGA的CCLK產生的時鐘進行的;因為使用的芯片時串行的配置芯片,所以只有一個數據信號口DO,連接到FPGA的DIN口(上圖沒有畫出),和上面的時鐘信號協同工作完成串行數據傳輸,每當CLK的上升沿鎖存數據,同時PROM內部的地址計數器自動增加;另外還有兩條控制信號線時INIT(連接PROM的OE/RESET)和DONE(連接PROM的CE),OE/RESET是為了確保每次重新配置前PROM的地址計數器復位;關于CE腳,官方資料說得也不是很詳細,以我個人的理解,CE應該是chip enable的縮寫,從它和FPGA的DONE腳連接我們不難推斷出,FPGA未配置完成時DONE=0,那么配置芯片PROM處于片選狀態,而一旦配置完成DONE=1,那么PROM就不再被選通,同時datasheet也說到這個管腳可以直接接地,就是一直片選中,但是這樣會使DATA口有持續的數據信號輸出,同時導致不必要的電流消耗;CEO腳這里不接,因為它在多個PROM的配置電路中時作為下一個PROM的OE端信號連接用的;CF信號時連接FPAG的PROG_B接口的,它的作用就是產生開始配置信號,它連接了一個上拉電阻,如果PROG_B產生低電平脈沖則PROM會重新開始一次配置,所以我們會在這條線上接一個按鍵到地,如果按鍵按下那么就會使能PROM重新配置FPGA;還有幾個信號接口TDI,TCK,TMS,TDO都是PROM和PC連接的信號,PC通過這些電路(通常接一片驅動隔離芯片后通過并口通信,這里不重點介紹了)下載數據到PROM中。

上面談及PROM的信號接口時都附帶的談到了FPGA的配置管腳。這里再做一些歸納性的說明。FPGA有7個專用的配置管腳(CCLK,DIN,PROG_B,DONE,HSWAP_EN,M0,M1,M2),4個專用的JTAG管腳(TDI,TCK,TMS,TDO),這些管腳是由VCCAUX專門供電的(該系列FPGA通常接VCCAUX=2.5V)。FPGA的M0,M1,M2腳是進行配置模式選擇用的,該電路主串模式下{M0,M1,M2}=000,如果時JTAG下載模式{M0,M1,M2}=101。上面沒有提及的HSWAP_EN管腳接地,則是用于設置當FPAG處于配置狀態下其它閑置管腳為上拉狀態,而如果該管腳接高電平,則FPAG處于配置狀態下其它閑置管腳浮空。所以為了減少FPGA配置過程的干擾,一般把此腳接地。

fpga相關文章:fpga是什么

電流傳感器相關文章:電流傳感器原理 上拉電阻相關文章:上拉電阻原理

評論