基于DSP的自適應濾波器的設計方案

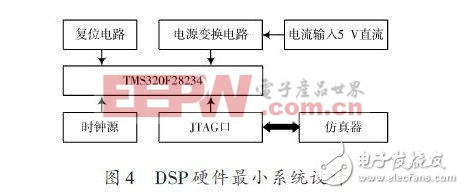

1.3 DSP的最小硬件系統設計

DSP的硬件最小系統設計包括DSP芯片、電源轉換電路、時鐘電路、復位電路、JTAG 仿真接口等,如圖4所示。

2 基于DSP 的自適應濾波器的軟件設計

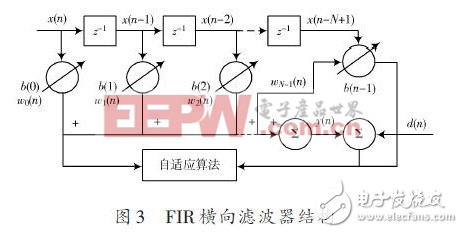

采用TMS320F28234實現自適應濾波器,自適應算法采用基本的LMS算法,濾波器的結構采用橫向FIR結構。

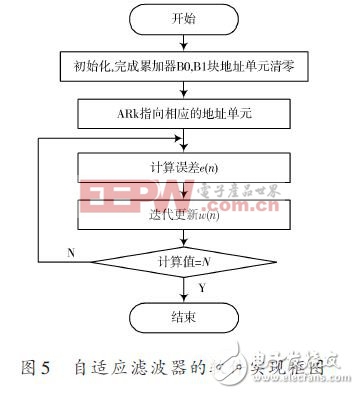

自適應濾波器的TMS320F28234的設計中,程序設計語言運用匯編語言,自適應濾波器程序設計流程如圖5所示。

3 仿真驗證

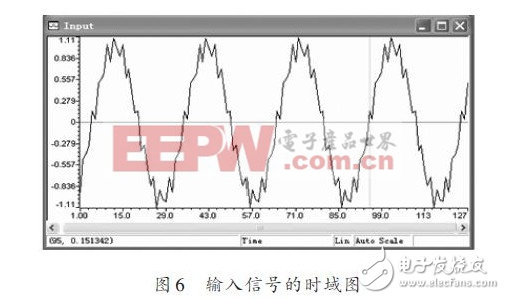

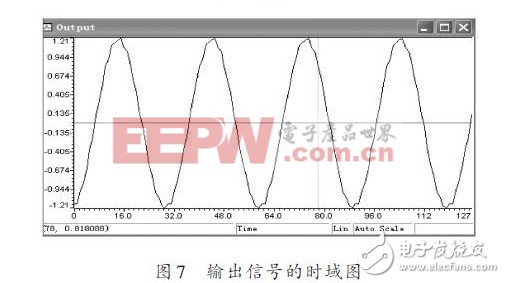

為了說明自適應濾波器的優越性,這里通過仿真結果來表明。通過引入一個已有的數據文件方式得到一個受到噪聲干擾的正弦波信號,該波形作為自適應濾波的輸入信號。自適應濾波程序在CCS 環境下編譯、鏈接、修改語法錯誤,編譯鏈接通過后,加載并連接程序,連接生成公共目標代碼文件,在線下載到DSP中運行。將編譯產生的可執行文件下載到 DSP芯片中后,經過運行得到時域圖,輸入信號的時域圖如圖6所示。

由圖6可以看到,低頻信號中疊加了有噪聲信號,導致低頻信號出現了較大的畸變。低頻的信號中疊加了比較多的高頻噪聲,只有進行高頻濾波才能夠得到比較好的原始低頻信號。在觀察輸出波形時,能夠看到輸出波形中僅剩余了低頻信號,濾除了高頻成分。通過圖6 和圖7的對比,輸入信號的高頻噪聲基本上得到了濾除。但是由于參數設置不夠精確等原因造成的高頻噪聲沒有得到完全消除,但是也很明顯的顯現了低通濾波的目的。

4 結語

評論