利用C2000 MCU實施并網微型太陽能逆變器(一)

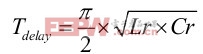

所以,最好是讓停滯時間位于Q1關閉和Q2打開之間,小于Tdelay,以實現部分ZVS狀態。

即使Lr中存儲能量不足以完全對開關電容Cr完全放電,從而最小化Q1和Q2的潛在電壓應力(并獲得更高的轉換器效率),我們必須小心地設計諧振電感Lr、諧振電容Cr和鉗位電容Cc的參數。

2.3.2.1 諧振電感Lr設計

在確定Lm值以后,可對諧振電感進行設計。如前所述,我們假設其值為Lm的一小部分(通常為Lm的5%到10%)。

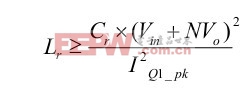

給定轉換器工作點和Cr值時,要實現ZVS,Lr的大小必須足以完全對開關電容放電。

Lr設計很難,因為諧振電容電壓(Vcr)為Lr值的函數,如下面方程式:

但是,在實際設計中,諧振電感電壓相對較小(相對于Vin+NVo),并且可求解實現ZVS狀態必需的Lr近似最小值:

在要求高輸出電壓的這種應用中,專門的輸出整流器軟開關特性比實現主開關ZVS要更為理想。

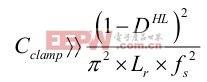

2.3.2.2 鉗位電容器Cc設計

根據Lr設計,選擇鉗位電容的值。鉗位電容器和諧振電感形成的諧振頻率足夠低,這樣,當開關關閉時,電源開關便不會出現過多的諧振振鈴。但是,使用過大的鉗位電容值,并不會帶來鉗位性能的改善,并且代價是更大容量(同時也更加昂貴)的電容器。一種較好的折中方法是,選擇一個電容器值,使鉗位電容器和諧振電感形成的諧振時間的一半,超出Q1的最大關閉時間。因此:

其中,DHL表示最大輸入電壓工作,fs為Q1和Q2的工作開關頻率。

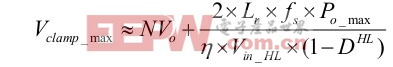

電容器額定電壓必須超出NVo,并且超出量為Lr的壓降:

鉗位電容器和諧振電感的諧振時間可通過下列方程式計算得到:

評論