FPGA+DSP的高速通信接口設計與實現

(2) 控制部分:由令牌轉換模塊和控制模塊組成,是整個設計的核心部分,完成對各部分的控制和與FPGA內部進行通信(通過CTL一組信號)。TS101的鏈路口通信握手是靠兩根時鐘信號驗證令牌指令完成,即當發送端驅動原本為高的LxCLKOUT信號為低電平,以此作為令牌請求向接收端發出。如果接收端準備好接收,則接收端驅動LxCLKIN為高;如果令牌發出6個時鐘周期后,LxCLKIN信號仍然為高,則肩動數據傳輸(以上時鐘信號都以發送端視角分析)。本設計中,令牌轉換模塊負責驗證令牌和發送令牌。這里要注意,由于用來驗證令牌低電平個數的時鐘信號(PLL_32ns)是由FPGA時鐘信號(CLK)通過鎖相環倍頻得到,與DSP鏈路口時鐘異步,故驗證令牌時,當計數器計到5個低電平時即可認為已達成通信握手,否則可能會丟失數據。達成握手后通知控制模塊向接收或發送緩存輸出控制信號,其中接收控制信號包括寫緩存時鐘和寫使能。發送控制信號包括讀緩存時鐘、讀使能和DSP中斷信號(DSP_IRQ),其中寫緩存時鐘通過對鏈路口時鐘分頻得到,讀緩存時鐘由鎖相環倍頻FPGA工作時鐘得到。

(3) 發送部分:與接收部分類似,也南編碼和緩存兩部分組成,相應的設計基本相同,這里不作過多介紹。由于DSP鏈路口每次傳輸數據個數的最小單位是4個32位字,即8個鏈路時鐘周期,所以發送時鐘廊該每8個時鐘周期一組,以湊夠128bit,避免傳輸錯誤,其中多余無效的數據DSP可以自行舍去。發送部分采用DSP外部中斷方式而不是鏈路口中斷方式通知DSP接收數據。

TS101的鏈路口通信協議要求鏈路口接收端在傳輸啟動一個周期后,將其LxCLKOUT拉低,若可以繼續接收,在下一個周期再將其拉高,以此作為連接測試。實際運行中發現,當FPGA接收數據時,可將LxCLKOUT信號一直驅動為高,不必做特殊的連接測試也能正確接收數據。另外,發送鏈路口數據時,由于發送緩存中已經對應仔好了要發送的8bit數據,故可以使用對FPGA時鐘信號(CLK)倍頻得到的PLL_16ns信號來讀發送緩存,讀出的數據即鏈路口發送數據,再對PLL_16ns信號的下降沿分頻得到鏈路口的發送時鐘信號。

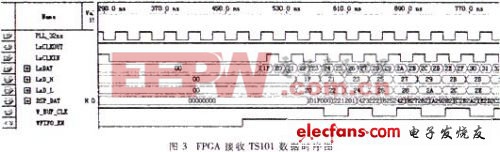

限于篇幅,本文只給出FPCA接收TS101數據的時序圖,如圖3所示。LxCLKIN、LxDAT[7..0]是DSP的鏈路口輸出時鐘和數據,LxCLKOUT是FPGA的回饋準備好信號。仿真中鏈路口數據采用1F-3E(十六進制)的32個8bit數據,即從2221201F到3E3D3C3B的8個32bit數據;PLL_32ns信號是FPGA內部鎖相環產生的與DSP鏈路口時鐘異步的32ns時鐘信號,用來校驗令牌指令;W_FIFO_EN信號足寫緩存使能信號,當令牌驗證后使能接收緩存;DSP_DAT信號是DSP通過鏈路門傳輸的32bit數據,通過對鏈路口數據的編碼得到;W_BUF_CLK信號由鏈路口時鐘分頻處理得到,將上升沿對應的32bit DSP數據寫入接收緩存,完成接收過程。

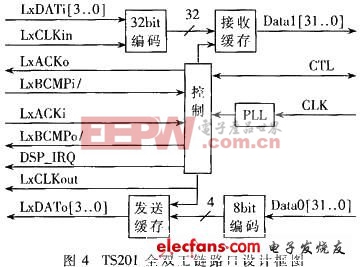

2.3 基于FPGA的TS201鏈路口設計

圖4給出了FPGA與TS201進行鏈路口通信的設計框圖。由于TS201的握手信號較多,所以相對TS101的鏈路口設計容易些。本設計FPGA時鐘50MHz,TS101核時鐘500MHz,鏈路口時鐘為DSP核時鐘的4分頻,采用4bit方式,單向實際數據傳輸速率為125MBps。

TS201的鏈路口數據和時鐘采LVDS信號,具有速率高、功耗低、噪聲小的優點。Cyclone系列芯片不僅支持LVDS信號,還集成了LVDS轉換模塊,這給設計提供了很大方便。應該注意的是,在硬件設計時LVDS信號兩極的PCB走線要匹配,并且注意匹配電阻網絡的接入。

TS201的鏈路口有1bit和4bit兩種傳輸方式,本文以4b

fpga相關文章:fpga是什么

通信相關文章:通信原理

評論