高速多模式RS編碼的設計方案

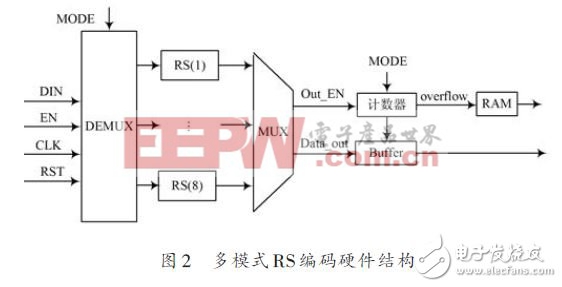

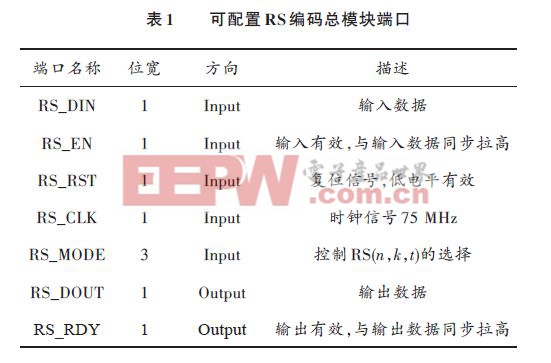

多模式RS 編碼模塊,根據MODE 信號對于可配置的RS 模塊進行實時的配置。圖2 為多模式RS 編碼在L-DACS1 中硬件實現結構圖,表1 為多模式RS 編碼器模塊端口說明。

根據協議規定,L-DACS1發射機使用歸零卷積碼,所以需要將RS編碼器的輸出數據末尾進行補零處理。因為卷積碼的約束長度為6位,因此需要補6個零。

RS 編碼后的數據放入緩存器中然后輸出。根據MODE 信號對于計數器進行選擇,計數器最大值時,將BUFFER 使能端置為低電平,同時激活ROM,順序輸出6個0值符號。然后計數器置為0,將BUFFER使能端拉至高電平。

3 多模式RS 編碼器仿真

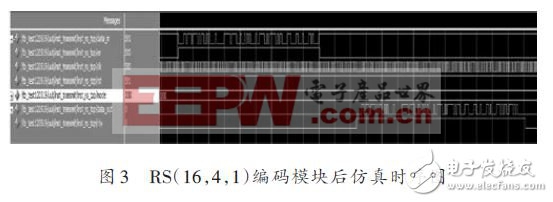

利用Verilog HDL 硬件描述語言對多模式RS 編碼器進行仿真,對工程文件進行綜合、布線和仿真,以RS(16,4,1)編碼為例進行分析,其后仿真結果如圖3所示。、

圖3 中,MODE 是模式控制信號,可根據該信號來選擇不同的RS編碼模式。data_in為模塊的輸入數據,每次連續輸入112 b數據;data_out為RS編碼后輸出數據,每次連續輸出134 b;rdy 為數據輸出有效標志位。

本次仿真RS(16,4,1)編碼,模式信號MODE為000.仿真其他模式RS編碼,改變MODE信號即可。

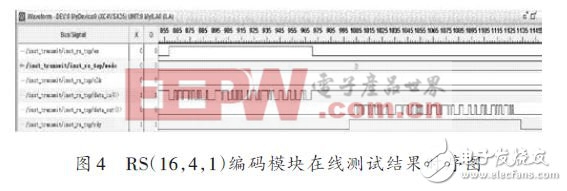

將仿真通過的工程文件使用ChipScope添加觀察信號采樣時鐘、觸發信號和待觀察信號后重新綜合、布局布線生成bit文件,下載到Xilinx公司的Virtex-5系列的XC5VLX110-F1153 型號的芯片后用ChipScope 進行在線測試,采用主時鐘75 MHz,得到測試結果如圖4所示。

圖4中,en表示輸入使能信號,data_in表示編碼之前的數據,data_out表示RS編碼后輸出數據,rdy表示輸出數據有效的信號,輸入時鐘頻率為75 MHz,采樣時鐘頻率為150 MHz.通過對比圖3的仿真結果和圖4的在線測試結果,可以驗證在高速的時鐘下設計的正確性。

4 結語

本文提出了一種基于L-DACS1系統中高速多模式RS 編碼的設計方案。本方案先闡述了L-DACS1系統中多模式RS編碼器的工作原理,利用FPGA設計實現了可以在高速多模式條件下正常工作的RS 編碼器。同時用Verilog HDL 硬件描述語言對此設計進行了仿真驗證,最后使用75 MHz的主時鐘頻率,在Xilinx 公司Virtex-5 系列XC5VLX110-F1153型號芯片下完成了硬件的調試,仿真及在線測試結果表明,達到了預期的設計要求,并用于實際項目中,以此證明該方案具有較強的實用性。

評論